5강. HDL(hardware description language), 베릴로그(verilog)

추천글 : 【논리설계】 논리설계 목차

1. wire vs reg [본문]

2. always@/initial [본문]

3. descriptions [본문]

4. 벡터 표시 [본문]

5. 하드웨어 구현 시 주의사항 [본문]

⑴ wire

① wire는 두 인스턴스를 연결하는 도선이다.

② wire는 실제 module 선언 시 input과 output으로 꼭 사용된다.

③ wire는 홀로 어떤 값을 저장할 수 없다; 정보의 통로 역할이기 때문

④ wire는 always@/initial 블록에서 =, <= 연산 시 왼쪽에 올 수 없다.

⑤ 좌변이 wire이고, 우변이 reg이면 wire가 값을 저장하는 게 돼 버리므로

⑥ always@/initial 블록 밖에서는 wire 연결 시 assign을 써야 한다.

⑦ always@/initial 블록 안에서는 assign은 쓸 수 없다.

⑧ assign 연산을 수행 시 wire 변수만 좌변에 올 수 있다.

⑨ wire는 combinational logic에서만 쓰인다.

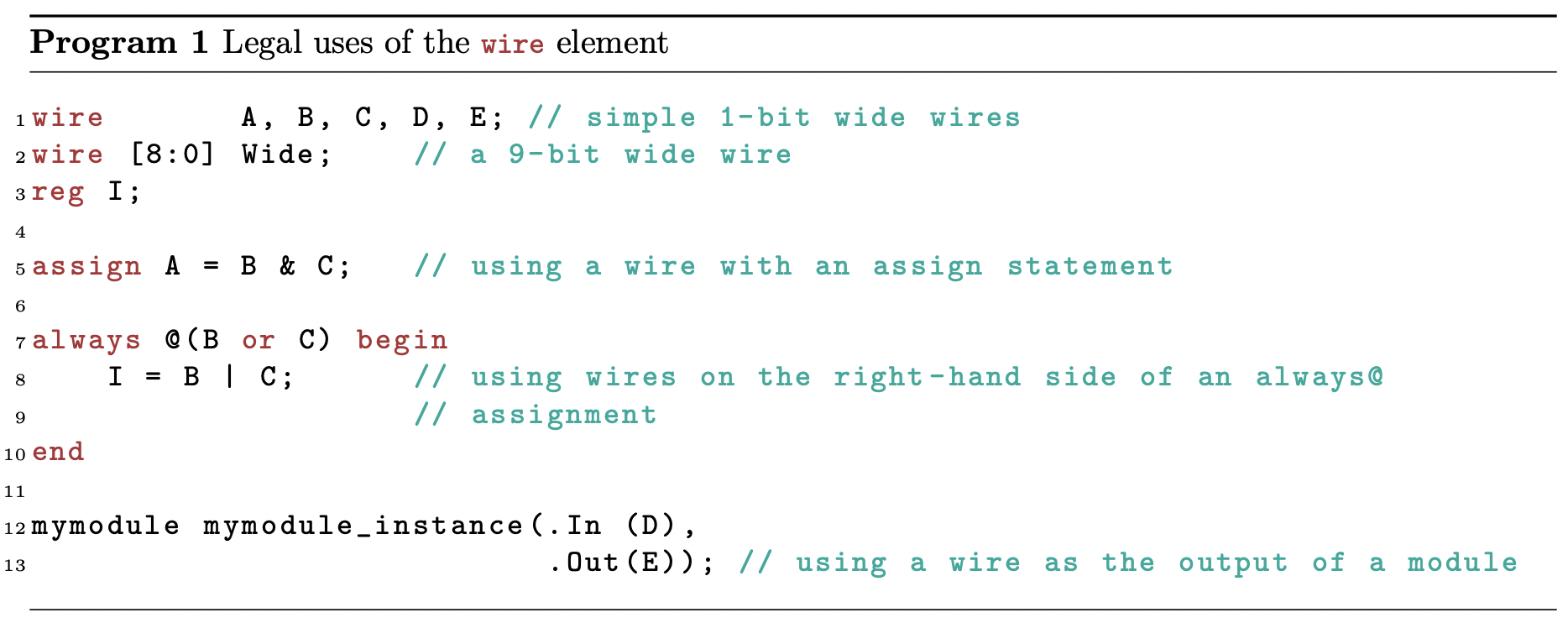

⑩ wire의 용례

Figure. 1. wire의 용례

⑵ reg

① reg는 값을 저장하는 변수로 flip-flop이나 latch가 쓰인다.

② input과 똑같은 이름의 reg 변수를 선언함으로써 자동으로 input과 연결될 수 있다.

③ reg는 output으로 연결될 수는 있으나, output wire와 연결될 수는 없다.

④ reg 변수가 input으로 사용될 수 없다.

⑤ always@/initial 블록에서 =, <= 연산 시 reg 변수만 좌변에 올 수 있다.

⑥ '<='가 포함된 문장을 비블록형 문장(non-blocking statement)이라고 한다.

⑦ '='가 포함된 문장을 블록형 문장(blocking statement)이라고 한다.

⑧ 반복 구간 안에서 비블록형은 동시에 처리되고, 블록형은 따로 처리된다.

⑨ reg는 assign 연산 시 왼쪽에 올 수 없다.

⑩ assign은 기본적으로 좌변의 wire를 우변에 연결한다는 의미이기 때문

⑪ always@/initial 블록 안에서는 있으나 마나 차이가 없다.

⑫ reg는 combinational logic과 sequential logic에서 모두 쓰인다.

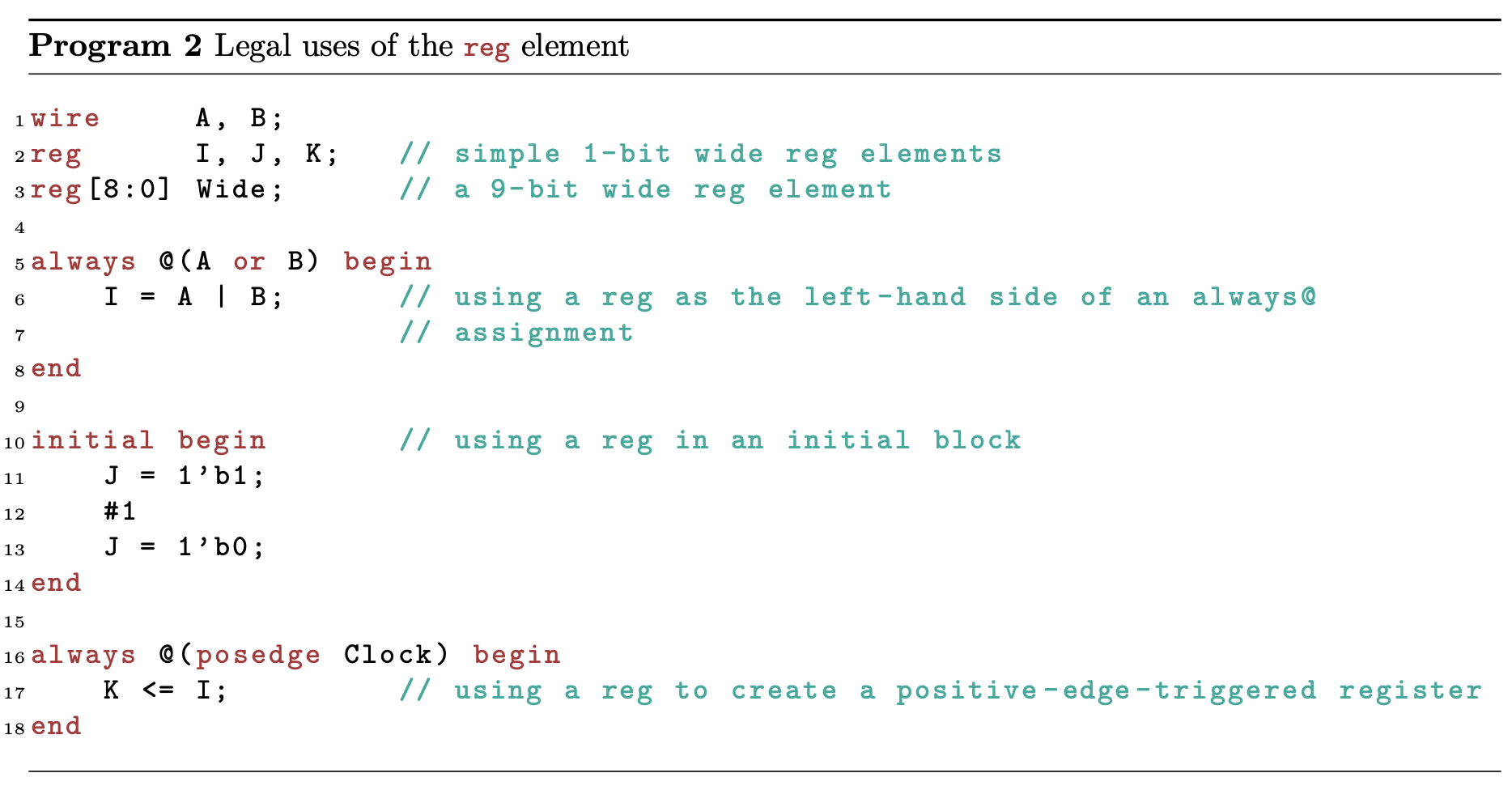

⑬ reg의 용례

Figure. 2. reg의 용례

⑴ 값의 저장, 논리함수 등은 반드시 always@/initial 블록 안에 있어야 한다.

⑵ initial은 맨 처음 1회, always@는 해당 조건이 만족할 때면 항상 실행되는 명령이다.

⑶ always@ (*) : 신호가 들어올 때.. () 값이 변할 때는 언제.. (posedge ##) (negedge ##)

3. descriptions [목차]

⑴ structural description : 모듈 및 gate를 조합해서 논리회로를 완성하는 방식

⑵ hierarchical description : 모듈 간의 포함관계 또한 설정할 수 있다.

⑶ data flow style description : 모듈 간의 wiring을 설정해서 논리회로를 완성하는 방식

⑷ behavioral(algorithmic) description : C 프로그래밍과 비슷한 방법

4. 벡터 표시 [목차]

⑴ [n-1 : 0]에서 [n-1]은 MSB, [0]은 LSB를 나타낸다.

⑵ 이러한 벡터표현도 가능하다.

⑶ .A({a[1], a[0]}) ⇔ .A({a[1:0]}) ⇔ .A(a[1:0])

5. 하드웨어 구현 시 주의사항 [목차]

⑴ 하드웨어 구현 시 시뮬레이션과 다르게 initial이 전혀 의미가 없다. initial 구문은 전부 지우자.

⑵ 레지스터에 값을 저장 시 반드시 비블록형 문장을 쓰도록 하자. (물론 블록형도 가능하지만.)

입력: 2016.10.07 20:24

'▶ 자연과학 > ▷ 논리설계' 카테고리의 다른 글

| 【Logic Design】 adder circuits (0) | 2016.10.10 |

|---|---|

| 【논리설계】 6강. Implementation Technology (3) | 2016.09.28 |

| 【논리설계】 4강. 조합논리의 파형 (0) | 2016.09.23 |

| 【Logic Design】 2-bit comparator (0) | 2016.09.17 |

| 【Logic Design】 door_lock (0) | 2016.09.11 |

최근댓글