6강. Implementation Technology

추천글 : 【논리설계】 논리설계 목차

1. standard gates [본문]

2. regular logic [본문]

3. two-level programmable logic [본문]

1. standard gates [목차]

⑴ 논리설계는 빠르게 트랜지스터 수준에서 논리 게이트 수준으로 올라감 (1960s)

⑵ gate packages (1970s)

① 논리 게이트 하나만 사고팔면 비경제적이므로 패키지로 묶어서 팔기 시작

② 예 : 14-pin IC; 6-inverters, 4 NAND gates, 4 XOR gates

⑶ cell libraries

① 특정 기능을 수행하도록 논리 게이트들을 특정 조합으로 묶어 놓은 라이브러리

② 널리 쓰이진 않고, 디자이너에 한해 이 라이브러리가 사용됨

⑷ 단점 : 디자인하기 어렵고, hazard/glitch를 야기할 수 있다.

2. regular logic [목차]

⑴ 논리 게이트에서 더 상위 수준의 기능을 수행하여 회로를 구성하는 데 용이함

⑵ 멀티플렉서(MUX, multiplexer) : 선택기(selector)라고도 함

① 2n개 입력을 받아, control line에 따라 한 입력만 선택(select)해서 출력하는 소자

② 회로도

Figure. 2. MUX의 회로도

○ input : output : select = 2n : 1 : n

○ 실제로는 위 AND-OR circuit를 NAND-NOR circuit로 바꿔서 쓴다.

○ S-o-P이므로 AND Gate 및 OR Gate를 NAND Gate로 대체하면 된다.

③ cascading MUX: 작은 MUX를 조합해서 큰 MUX를 만들 수 있음

Figure. 3. 4:1 8:1 MUX를 cascading하는 두 가지 방법

④ n 변수 함수는 2n-1 : 1 MUX로 구현할 수 있음

Table. 1. 3변수 함수를 2 selects MUX로 구현하는 과정

○ 2n : 1 MUX

F = 1(A'B'C')+0(A'B'C)+0(A'BC')+1(A'BC)+1(AB'C')+1(AB'C)+0(ABC')+1(ABC)

○ 2n-1 : 1 MUX

F = C'(A'B')+C(A'B)+1(AB')+C(AB)

○ C가 아닌 A, B에 대해서도 전개해 보면 굳이 complement(ex. C')을 쓰지 않아도 된다.

○ Data line에서 Gate를 잘 응용하면 더 작은 MUX로도 구현할 수 있다.

⑤ 2:1 MUX는 AND Gate와 OR Gate를 구현할 수 있다.

Figure. 4. AND Gate와 OR Gate를 2:1 MUX로 구현하는 방법

⑥ 응용

⑶ DEMUX(demultiplexer)

① 1 bit 입력을 받아, control line에 따라 2n개의 출력단자 중 하나에만 출력하는 소자

② 회로도

○ input(G) : output(O) : select(S) = 1 : 2n : n

○ single data input을 보통 'enable'이라고 한다.

○ 실제로는 위 AND-OR circuit를 NAND-NOR circuit로 바꿔서 쓴다.

○ high-active enable이 low-active enable이 된다.

○ AND Gate를 NOR Gate로 바꾸고, select의 위치를 적절히 바꾼다.

Figure. 7. AND DEMUX를 NAND DEMUX로 바꾸는 과정

③ cascading DEMUX: 작은 DEMUX를 조합해서 큰 DEMUX를 만들 수 있음

Figure. 8. 32:1 DEMUX를 cascading하는 방법

④ 응용 1 : ROM(아래 참고)

⑷ 인코더(encoder)

① 정의

○ 아날로그 신호를 디지털 코드(이진 코드)로 부호화(encoding)하는 소자

○ 2n 비트의 입력을 n 비트의 출력으로 전환시켜 주는 소자

○ 응용 : 주어진 입력의 주소값을 출력. 이진수, 즉 BCD를 출력

② 4-to-2 bit encoder에 대한 truth table

Figure. 9. 4 × 2 encoder의 회로도와 진리표

○ 단점 1. 입력이 2개 이상이면 에러가 발생함

○ 단점 2. 입력이 모두 0이면 애매한 출력을 발생시킴 (ambiguity)

○ 두 개의 단점을 보완하기 위해 priority encoder가 대두됨

③ priority encoder (p-encoder)

○ 정의 : 단자들에 랭크를 부여하여 모든 조합의 입력에 대해 출력을 내도록 한 소자

○ 8-to-3 bit priority encoder에 대한 truth table

Figure. 10. priority encoder의 회로도와 진리표

○ 8-to-3 bit priority encoder에 대한 logic circuit

Figure. 11. 8-to-3 bit priority encoder의 회로도

○ 추가로 입력단자가 모두 0인 경우에만 0이 되는 출력단자를 두어 기존 encoder의 단점 2를 보완시킴

④ 예 1. 나침반에서의 encoder의 응용

Figure. 12. 나침반에서의 encoder의 응용

⑤ 예 2. IRQ(interrupt requests)

○ CPU가 인터페이스들과 우선순위에 따라 통신하는 것

○ 비주류 인터페이스를 낮은 우선순위에 두면 정작 필요할 때 쓸 수 없음

⑥ 예 3. rotary encoder : shaft encoder라고도 함

○ rotary encoder에는 shaft로 연결된 회전판이 있음 (왼쪽 그림)

○ 빛을 통과시키면 0, 통과시키지 못하면 1로 인식하여 회전을 코드로 변환함

○ (주석) 세 개의 동심원의 높이가 달라서 특정 시선 방향에 대한 각 원의 코드를 읽을 수 있는 듯

○ 이진코드를 그레이 코드로 변환할 때 사용함

⑦ 예 4. incremental encoder : 선형 또는 회전 변위를 디지털 코드 또는 펄스 신호로 바꾸는 인코더

Figure. 14. incremental encoder

⑸ 디코더(decoder)

① n 비트의 코드화된 정보를 그 코드의 각 비트 조합에 따라 2n개의 출력으로 번역하는 회로

② DEMUX에서 control line이 input line이 된 것이 decoder

③ 응용 : cascaded decoder

Figure. 15. 2개의 2-to-4 decoder를 이용한 3-to-8 decoder

⑹ 일반적인 설명

① DEMUX로 MUX를 구현할 수 있다. (즉, DEMUX가 좀 더 유연하다.)

○ 모든 output 단자에 AND Gate를 달고 그 출력단자를 선택적으로 OR Gate에 연결

② 실제로 MUX에도 enable이 달려 있다.

3. two-level programmable logic [목차]

⑴ 실제로 스마트폰 CPU을 설계하는 데 기존의 것을 재사용하면 보통 1년, 새로 만들면 2년이 걸림

⑵ PLA(programmable logic array)

① 프로그래밍이 가능한, 이미 완성된 AND arrays, OR arrays 세트

○ Sum-of-Product를 구현한다.

○ 실제로는 NAND-only circuit로 구성돼 있다.

② 회로 설계 과정

○ fuse 방식 : 원래는 활성화 돼 있고, 원하지 않는 교차점을 비활성화시키는 방식

○ anti-fuse 방식 : 원래는 비활성화 돼 있고, 원하는 교차점을 활성화시키는 방식

○ 프로그래밍을 수행한 뒤 모든 교차점을 활성화/비활성화 하여 원하는 교차점만 남긴다.

○ AND Gate의 입력단자의 경우 비활성화 시 voltage-high(1)로 연결해야 한다.

○ OR Gate의 입력단자의 경우 비활성화 시 voltage-low(0)로 연결해야 한다.

○ 만약 교차점이 남는다면 0과 연결한다.

③ technology mapping

○ AND Gate 수가 제한돼 있어서 AND Gate의 출력항의 경우의 수를 줄이기 위한 시도

○ AND Gate의 입력 단자의 수는 최초 입력을 위한 비트값을 의미하므로 고정돼 있음

○ OR Gate의 출력 단자의 수는 최종 출력을 위한 비트값을 의미하므로 고저돼 있음

○ AND Gate의 출력항의 수는 논리회로를 어떻게 설계하느냐에 따라 달라짐

○ 예시 : 7-segment

| C0 = A + BD + C + B'D' C1 = C'D' + CD + B' C2 = B + C' + D C3 = B'D' + CD' + BC'D + B'C C4 = B'D' + CD' C5 = A + C'D' + BD' + BC' C6 = A + CD' + BC' + B'C total term: 16 |

C0 = BC'D + CD + B'D' + BCD' + A C1 = B'D + C'D' + CD + B'D' C2 = B'D + BC'D + C'D' + CD + BCD' C3 = BC'D + B'C + B'D' + BCD' C4 = B'D' + BCD' C5 = BC'D + C'D' + A + BCD' C6 = B'C + BC' + BCD' + A total term: 9 |

⑵ PAL(programmable array logic)

① AND array와 OR array 사이의 교차점은 고정돼 있고, 입력과 AND array 사이를 조절한다.

○ 즉, 입력단자와 AND array 사이의 교차점만 프로그래밍할 수 있다.

○ 현재 기준, OR Gate의 최대 입력단자 수를 4개로 제한한다.

② 프로그래밍에 제약이 있으나 더 빠르게 작동할 수 있다. (∵ fuse/anti-fuse 횟수가 ↓)

③ OR Gate의 최대 입력의 제한으로 컴파일러의 도움으로 multi-level로 설계하는 경우가 많음

| C0 = A + BD + C + B'D' C1 = C'D' + CD + B' C2 = B + C' + D C3 = B'D' + CD' + BC'D + B'C C4 = B'D' + CD' C5 = A + C'D' + BD' + BC' C6 = A + CD' + BC' + B'C |

C0 = C3 + A'BX' + ADY C1 = Y + A'C5' + C'D'C6 C2 = C5 + A'B'D + A'CD C3 = C4 + BDC5 + A'B'X' C4= D'Y + A'CD' C5 = C'C4 + AY + A'BX C6 = AC4 + CC5 + C4'C5 + A'B'C X = C' + D' Y = B'C' |

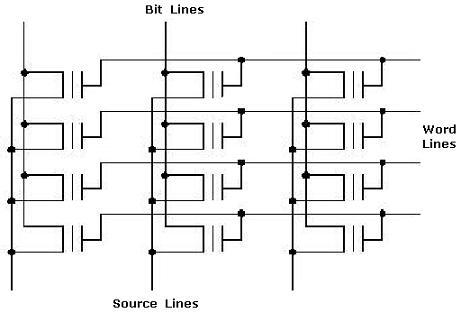

⑶ ROM(read-only memory)

① DEMUX를 응용하여, 2차원 array set을 구성해 저장된 값을 읽어들인다.

○ 2n × m ROM : address가 n-bit이고, word가 m-bit인 ROM

○ 입력값은 원하는 데이터가 저장돼 있는 주소값(address)이다.

○ 최종 출력값은 저장된 데이터이다.

② PLA와 비슷하지만, 오직 AND Gate로만 구성돼 있다. (실제론 NAND Gate)

③ ROM 구조

○ 1st. ROM 표면의 유리창을 통해 자외선을 쐬어주어 초기화시킨다. (EPROM/EEPROM)

○ 자외선은 전자가, 높은 퍼텐셜을 뚫고 이동하는 터널링 효과를 일으킨다.

○ 2nd. 이제 ROM 내 모든 트랜지스터는 평범한 nMOS이다.

○ 3rd. 특정 주소에 메모리를 쓸 때 특정 트랜지스터 내 FG에 전자를 저장시킨다.

○ FG는 트랜지스터에서 Gate와 bulk Si 사이에 떨어진 채로 존재한다.

○ FG 내 전자가 FG를 벗어나려면 공기층을 건너뛰어야 하므로 높은 에너지 필요

○ 4th. i번째 주소가 1이 되면 1, 2번째가 OFF이고, 나머진 ON이므로 0011 출력

○ FG 내 전자가 있으면 Gate에 (+)가 와도 그 효과를 상쇄시킨다.

○ FG 내 전자가 없으면 enabled, 있으면 disabled라고 한다.

○ 위쪽의 1은 voltage-HIGH이고,아래쪽이 output(word)이다.

○ 5th. j번째 주소가 1이 되면 2, 4번째가 OFF이고, 나머진 ON이므로 0101 출력

○ 최근에는 트랜지스터를 (차곡차곡 쌓아서) 3D로 배열하여 메모리 용량을 높임

④ ROM 종류

○ MROM(mask ROM) : 사용자가 내용을 바꿀 수 없는 ROM

○ 장점 : 대용량의 경우 저렴할 수 있음

○ 단점 : 유닛당 가격은 비쌈

○ 예 : mathematical table, character generator code 등에 사용함

○ PROM(programmable ROM) : 일부 사용자가 내용을 바꿀 수 있는 ROM

○ 제작 과정에서 프로그래밍 되지 않고, 사용자가 프로그래밍을 함

○ 일단 프로그래밍 되면 내용은 바뀌지 않음

○ fusible ink를 사용함 (예 : firmware, BIOS)

○ 장점 : MROM보다 가격이 저렴함

○ 예. Intel 7641 : bipolar PROM. 512 × 8 memory

○ EPROM(erasable PROM) : 자외선에 의한 전자 흥분으로 내용을 지울 수 있는 PROM

○ MOSFET의 일종

○ program process : 20 ~ 50 V의 전압을 50 ms 동안 인가

○ erase process : UV로 15-30분간 조사하여 전체 게이트의 전하를 제거함

○ 예. Intel 2716 : NMOS EPROM. 2K × 8 memory

○ EAROM(electrically alterable ROM) : 전기적으로 내용을 바꿀 수 있는 PROM

○ EEPROM(electrically EPROM) : 전기적으로 내용을 지울 수 있는 PROM

○ 1980년도에 EPROM을 개선하여 개발됨

○ program process : 게이트와 드레인 사이에 21 V 정도의 전압을 인가

○ read process : flash memory와 동일한 원리

○ erase process : 회로를 뒤집음. 10 ms 소요

○ 예. Intel 2816 : 2K × 8 memory (1981)

○ 플래시 메모리(flash memory) : 블록 단위로 지정해서 지울 수 있는 EEPROM

○ 저장용량이 큰 데이터 저장형(NAND타입)과 처리 속도가 빠른 코드 저장형(NOR타입)으로 분류

○ 메커니즘 : floating gate의 충전 및 방전

○ access time < 100 ㎱

○ write time < 10 ㎲

○ power supply < 10.0 V

○ erase time : ~ ㎳

○ # of RD/WT : 105 ~ 107

○ data retention time : ~ 10 years

○ operation current : ~ 10 ㎃

○ standby current : 10 ㎂

○ density : very large(@NAND)

⑤ 예 : CD ROM

⑷ 각 소자의 장단점

① price : (cheap) ROM < PAL < PLA (expensive)

○ ROM : 대량생산이 가능하므로 가장 싸다.

○ PLA : 디자인이 굉장히 복잡하고, 더 정교한 툴이 필요하다.

② speed on making : (fast) PAL > ROM > PLA (slow)

○ PAL : ROM보다 크기가 작은 programmable plane 하나

○ PLA : programmable plane 두 개

③ design time : (fast) ROM > PLA > PAL (slow)

○ ROM은 brute-force로 모든 조합의 minterm을 다루므로 고민할 필요가 없다.

○ PAL은 최대한 product-term을 줄여야 한다.

④ flexibility : ROM > PLA > PAL

○ ROM은 모든 함수를 구현할 수 있다.

○ PLA는 AND gate의 개수에 제약을 받는다.

○ PAL은 AND gate의 개수와 fixed OR plane에 제약을 받는다.

⑤ ROM의 단점

○ 부피가 가장 크다.

○ 입력단자가 하나 증가하면 ROM의 크기는 두 배가 된다.

○ don't-care의 장점을 잘 활용하지 못한다.

입력: 2016.09.30 15:16

'▶ 자연과학 > ▷ 논리설계' 카테고리의 다른 글

| 【논리설계】 7강. 클럭과 메모리 (0) | 2016.10.26 |

|---|---|

| 【Logic Design】 adder circuits (0) | 2016.10.10 |

| 【논리설계】 5강. 하드웨어 기술 언어 (0) | 2016.09.28 |

| 【논리설계】 4강. 조합논리의 파형 (0) | 2016.09.23 |

| 【Logic Design】 2-bit comparator (0) | 2016.09.17 |

최근댓글