7강. 클럭과 메모리(clock and memory)

추천글 : 【논리설계】 논리설계 목차

1. clock [본문]

2. latch [본문]

3. flip-flop [본문]

4. register [본문]

5. ROM [본문]

6. RAM [본문]

7. flash memory [본문]

8. 메모리 성능 비교 [본문]

9. 동기화 [본문]

1. clock : oscillator라고도 함 [목차]

⑴ 정의 : gate들의 delay로 일정시간의 주기를 갖도록 하는 소자

⑵ 구현 1. NAND gate를 이용한 oscillator 회로도

① 회로도

Figure. 1. NAND Gate를 이용한 oscillator 회로도

② NAND-oscillator의 파형

Figure. 2. NAND-oscillator의 파형

2. 래치(latch) [목차]

⑴ 정의 : 입력 신호가 인가되는 순간 바로 출력에 반영되는 기억소자

① 특징 1. level-sensitive : enable 또는 clock 신호 값의 수준(level)에 맞추어 동작. 즉, 구간의 형태로 반응함

② 특징 2. asynchronous : 시스템의 clock과 무관하게 출력에 반영됨

○ clock-gated latch의 경우 synchronous로 볼 여지가 있어서 애매함

③ 래치 소자에는 삼각형 표시가 없음 : 플립플롭과 차이가 있음

④ 단점 : latch는 입력신호가 곧장 출력으로 전해지기 때문에 noise 및 glitch에 매우 취약

○ 즉, enable이 1일 때 신호가 노이즈를 일으켰다면 의도치 않은 노이즈 신호가 그대로 전달됨

⑤ (참고) latch는 빗장 또는 걸쇠라는 의미를 가짐

⑵ 종류 1. bistable circuit : 가장 단순한 latch

Figure. 4. cross-coupled inverters를 응용한 가장 단순한 메모리 회로도

① stored value = load' ● remember + load

② load = 0, remember = 0인 경우 stored value은 floating을 함

⑶ 종류 2. cross-coupled inverter

Figure. 5. cross-coupled inverter

⑷ 종류 3. R-S latch : SR latch라고도 함

① 구현 1. 트랜지스터를 이용한 R-S latch

Figure. 6. 트랜지스터를 이용한 R-S latch

② 구현 2. NOR 게이트를 이용한 R-S latch : R-S latch의 가장 일반적인 형태

Figure. 7. NOR R-S latch를 구현하는 방법

③ 구현 3. NAND 게이트를 이용한 R-S latch : NOR R-S latch에서 드 모르간 법칙에 의해 전환

Figure. 8. NAND R-S latch를 구현하는 방법

④ (참고) NAND R-S latch를 다음과 같이 표현하기도 함 : 상태표가 다소 달라지므로 조심해야 함

Figure. 9. NAND R-S latch

○ R = 1, S = 1인 경우에 Hold이고, R = 0, S = 0인 경우는 허용되지 않음

○ R = 0, S = 1인 경우에 reset 기능이 활성화 됨 : 0일 때 활성화되므로 active low

○ R = 1, S = 0인 경우에 set 기능이 활성화 됨 : 0일 때 활성화되므로 active low

○ (주석) 일반적으로 active high를 선호하기 때문에 위와 같이 상태표가 뒤집힌 회로는 잘 쓰지 않음

⑤ 상태표(state table) 또는 여기표(excitation table)

| S | R | . | NOR | NAND | ||

| Q(t+Δ) | Q’(t+Δ*) | Q(t+Δ) | Q’(t+Δ*) | |||

| 0 | 0 | Hold | not Q(t) | not Q’(t) | not Q’(t) | not Q(t) |

| 0 | 1 | Reset | 0 | 1 | 0 | 1 |

| 1 | 0 | Set | 1 | 0 | 1 | 0 |

| 1 | 1 | Not allowed | 0 | 0 | 1 | 1 |

Table. 1. R-S latch의 상태표

○ NOR R-S latch에서 R = S = 0이면 bistable circuit의 형태가 됨

○ Q와 Q'이 결정되는 시간은 차이가 있음을 명심 (Δ ≠ Δ*) : 이것은 진리표를 작성해 보면 쉽게 알 수 있음

⑥ R-S latch의 출력 파형

Figure. 10. R-S latch의 출력 파형

⑦ 단점 : 레이스(race) 현상. (R, S) = (1, 1)이 된 뒤 R = S = 0이 되면 출력은 발진을 함

○ 예를 들면 (Q, Q') = (0, 0) → (1, 1) → (0, 0) → (1, 1) ···과 같이 변할 수 있음

○ 실제로는 Q, Q'의 타이밍 차이로 인해 Q가 어떤 값일지 불확실함

○ (참고) 일단 (R, S) = (1, 1)인 순간 자체는 문제가 되지 않음

○ (참고) (R, S) = (1, 1)이 된 뒤 (R, S) = (1, 0) 또는 (0, 1)이 돼도 문제가 되지 않음

⑧ 응용 1. 기계적 진동에 의한 contact bounce를 제거하기 위하여 R-S latch를 사용함

Figure. 12. contact bounce를 제거하기 위한 R-S latch

Figure. 13. switch bounce noise elimination

⑨ 응용 2. 화재 경보기

Figure. 14. 화재 경보기에 사용되는 RS latch

○ 디폴트 : SW1은 닫혀 있어서 R = 0이고 빛은 계속 비춰져서 트랜지스터 스위치가 닫혀 S = 0임

○ 연기로 인해 빛이 가려진 경우 : 순간적으로 S = 1이 되어 Alarm 회로가 작동함

○ 빛이 가려졌다가 다시 비춰진 경우 : R = S = 0이므로 결과를 Hold하여 Alarm 회로가 지속적으로 작동함

⑸ 종류 4. gated R-S latch

① gated R-S latch의 회로도 : 다음은 NOR R-S latch를 이용한 회로. NAND R-S latch를 이용할 수도 있음

Figure. 15. gated R-S latch의 회로도

② gated R-S latch의 출력 파형 : enable 또는 gate가 1인 경우에만 R, S의 신호가 R-S latch로 전달. 0인 경우 Hold

Figure. 16. gated R-S latch의 출력 파형

○ 이로 인해 R, S의 값이 불안정적일 때 enable이 1이 되어서는 안 됨

○ enable이 clock의 형태로 주어지더라도 pulse detector circuit이 없으면 latch에 해당함

○ (주석) 이것을 이해하기까지 상당히 오래 걸렸음

③ (참고) R = S = 1일 때의 문제를 다음과 같이 해결할 수 있음

Figure. 17. R = S = 1일 때의 문제를 해결한 gated R-S latch의 회로도

⑹ 종류 5. gated D latch (gated data latch) : typical data latch라고도 함

① 정의 : gated SR latch의 입력을 묶어서 허용되지 않는 값이 없도록 만든 latch

○ R과 S 단자 사이에 인버터를 장치함

○ (R, S) = (1, 1)이 입력되어 Q의 값이 모호하게 되는 상태를 피함

○ 일반적으로 가장 많이 이용되는 래치

○ (주석) gate가 없는 D latch는 거의 쓰지 않는 듯

② 구현 1. NAND gate를 이용한 gated D latch

Figure. 18. gated D latch의 회로도

③ 구현 2. cross-coupled inverter와 transmission gate를 이용한 gated D latch

Figure. 19. cross-coupled inverter와 transmission gate를 이용한 gated D latch

④ gated D latch의 출력 파형 : enable이 HIGH일 때 출력 Q는 입력 D를 따름

Figure. 20. gated D latch의 출력 파형

○ EN = 1일 때 Q는 입력 D를 그대로 출력하므로 transparent latch라고도 함

3. 플립플롭(flip-flop) [목차]

⑴ 정의 : 스위치 및 clock의 edge 신호에 맞추어 입력이 출력에 반영되는 기억소자

① 특징 1. edge-sensitive : 클럭의 edge 신호에 맞추어 소자가 반응함

② 특징 2. synchronous : clock에 맞추어 신호가 바뀜

○ 비동기 입력에 edge-sensitive하게 반응하는 경우도 있을 수 있어서 애매함

③ 플립플롭 소자에는 삼각형 표시가 있음 : 래치와 차이가 있음. 다이나믹 기호라고 함

④ 래치와 달리 입력 신호의 glitch에 영향을 받지 않음

○ edge 근방에서 glitch가 일어나면 운 나쁘게 문제 발생

⑵ 종류 1. single-stage flip-flop : master/slave flip-flop과 달리 pulse detector circuit을 필요로 함

① pulse detector circuit : clock의 edge에 맞추어 잠깐 동안 활성화되는 회로

○ pulse transition detector회로라고도 함

○ 즉, pulse detector circuit은 일종의 glitch(spike)를 의도적으로 발생시킴

② pulse detector circuit의 개요도

Figure. 22. pulse detector circuit의 개요도

③ positive edge triggered pulse detector circuit : rising edge에 맞추어 동작. pos-edge triggered라고도 함

Figure. 23. positive edge triggered pulse detector circuit

④ negative edge triggered pulse detector circuit : falling edge에 맞추어 동작. neg-edge triggered라고도 함

Figure. 24. negative edge triggered pulse detector circuit

⑤ (참고) pulse detector circuit의 표시를 생략하는 경우도 많음

⑶ 종류 1-1. (single-stage) R-S 플립플롭

① 구조 : 다음은 NAND R-S latch를 이용한 회로. NOR R-S latch를 이용할 수도 있음

② 정의 : clock gated R-S latch에서 clock과 래치 사이에 pulse detector circuit이 연결된 형태

③ 단점 : 여전히 레이스 현상이 해결되지 않음

⑷ 종류 1-2. (single-stage) D 플립플롭

① 정의 : clock gated D latch에서 clock과 래치 사이에 pulse detector circuit이 연결된 형태

② D 플립플롭의 회로도

② D 플립플롭의 출력 파형 : 점선은 edge-triggering을 의미하는 게 아님

③ 응용 : frequency divider

Figure. 28. D 플립플롭을 이용한 frequency divider

⑸ 종류 1-3. (single-stage) JK 플립플롭

① JK 플립플롭의 회로도

② JK 플립플롭의 상태표 : 초기화가 반드시 필요함

Figure. 30. JK flip-flop의 회로도와 특성표

③ JK 플립플롭의 출력 파형

Figure. 31. pos-edge JK flip-flop의 출력 파형

Figure. 32. neg-edge JK flip-flop의 출력 파형

Figure. 33. neg-edge JK flip-flop의 출력 파형

④ 응용 : frequency divider

Figure. 34. JK flip-flop을 이용한 frequency divider

○ clock의 주기를 바꾸는 데 이용됨

○ counter를 이용하여 특정 시간 뒤에 edge가 생기도록 조절한다. (preferred)

⑤ 비동기 입력 (single-stage) JK flip-flop의 회로도

Figure. 35. 비동기 입력 (single-stage) JK flip-flop의 회로도

○ preset : Q = 1, Q' = 0이 되도록 함. 일반적으로 preset'으로 제공하여 preset' = 0일 때 작동함 (∵ 저렴하기 때문)

○ clear : Q = 0, Q' = 1이 되도록 함. 일반적으로 clear'으로 제공하여 clear' = 0일 때 작동함 (∵ 저렴하기 때문)

○ (참고) 위와 같이 preset' 또는 clear'으로 제공하는 것을 active low operation이라고 함

○ preset'과 clear'이 모두 0이 되는 일은 없음

⑥ 비동기 입력 (single-stage) JK flip-flop의 출력 파형

Figure. 36. 비동기 입력 (single-stage) JK flip-flop의 출력 파형

⑹ 종류 1-4. (single-stage) T flip-flop : toggle RS flip-flop이라고도 함

① T flip-flop의 회로도 : JK flip-flop에서 두 입력선을 하나로 묶은 것임

② T flip-flop의 상태표 : 1 bit 입력과 1 bit 출력을 갖는 회로로 입력이 1이면 toggle, 0이면 hold를 함

③ T flip-flop의 출력 파형

Figure. 38. T flip-flop의 출력 파형

⑺ 종류 2. master/slave flip-flop

① 정의 : 두 개의 latch를 주종관계로 붙여서 플립플롭으로 만든 것

② single-stage flip-flop과 달리 pulse encoder circuit을 필요로 하지 않음

③ master/slave flip-flop, double-stage flip-flop, delayed flip-flop 등으로도 불림

④ 특징 : 입력 신호를 edge-sensitive하게 인식한 뒤 0.5T만큼 딜레이된 뒤에 출력에 반영됨 (아래 참조)

⑻ 종류 2-1. master/slave R-S flip-flop : 기본적으로 race 문제가 해결된다.

① posedge F/F : clock의 rising edge에서의 P, P'의 정보가 slave로 전달

② negedge F/F : clock의 falling edge에서의 P, P'의 정보가 slave로 전달

○ clock의 해당 edge에서만 R, S가 출력에 전달된다고 간주 가능

○ negdege F/F는 posedge F/F에서 CLK를 CLK'으로 대체한 회로

③ master/slave R-S flip-flop의 회로도

Figure. 39. master-slave R-S flip-flop의 회로도

④ 장점 : R-S latch와 single-stage R-S flip/flop에서 발견되는 레이스 현상이 약간 해결됨

○ 이유 : master stage에서 레이스 현상이 있어도 edge에서만 반응하는 slave stage에 큰 문제를 일으키지 않음

○ (주석) 레이스 현상을 완전히 해결하는 것은 아닌 것 같음

○ (주석) 레이스가 있고 나서 R = S = 0이라면 그 영향이 slave stage에서도 나타날 것이기 때문

⑤ 단점 : 1's catching problem. R-S 플립플롭에서 Hold 기능 때문에 생기는 문제점이 여전히 발견됨

Figure. 40. neg-edge master-slave R-S latches의 단자별 파형

실제 파형에 가깝게 그렸기 때문에 edge에 완벽하게 대응되지 않음

0.5T만큼 딜레이된다는 것을 알 수 있음

○ 1st. R = S = 0이었다가 S or R이 순간적으로 1로 glitch를 일으킴

○ 2nd. 하필 그 glitch가 duty cycle과 접점을 가짐

○ 3rd. 그 접점 때문에 P, P'의 값이 바뀜

○ 4th. 다시 R = S = 0이 되므로 P, P'은 바뀐 값을 Hold를 함

○ 5th. CLK의 negedge에서 바뀐 P, P'은 Q, Q'에 전달됨

⑼ 종류 2-2. master/slave D flip-flop : double-stage D FF라고도 함

① 구현 1. 두 개의 gated R-S latch를 이용한 neg-edge master/slave D flip-flop

Figure. 41. 두 개의 gated R-S latch를 이용한 neg-edge master/slave D flip-flop

② 구현 2. 간소화된 neg-edge master/slave D flip-flop : 실제로 많이 사용함

Figure. 42. 간소화된 neg-edge master/slave D flip-flop

○ 단계 1. CLK = 1 → (c, d) = (0, 0) → (R, S) = (0, 0) → Hold

○ 단계 2. Falling Edge → e = D' (∵ d = 0) → (b, d) = (D, D) (∵ c = 0) → c = D' → (R, S) = (D', D)

③ 출력 파형 : D flip-flop과 같이 1's catching problem이 없음

Figure. 43. pos-edge master/slave D flip-flop의 출력 파형

0.5T만큼 딜레이된다는 것을 알 수 있음

Figure. 44. pos-edge master/slave D flip-flop의 출력 파형

0.5T만큼 딜레이된다는 것을 알 수 있음

④ 장점 : master/slave D 플립플롭은 master/slave R-S 플립플롭의 1's catching problem을 해결하기 위해 도입

○ 기본적으로 pulse detector circuit을 이용하는 single-stage R-S flip-flop은 1's catching problem을 일으키지 않음

○ master/slave R-S flip-flop이 Hold 기능이 있고, pulse-detector circuit을 이용하지 않기 때문에 일어나는 문제점

○ D 플립플롭의 해결방법 : 입력이 (0, 0)인 경우를 제외시켜 버림

○ 모든 경우에 clock의 해당 edge에서만 D의 정보가 출력에 반영된다고 간주 가능

⑤ 비동기 입력 master/slave D flip-flop의 회로도

Figure. 45. 비동기 입력 master/slave D flip-flop의 회로도

○ reset : Q = 0, Q' = 1이 되도록 함. 일반적으로 reset'으로 제공하여 clear' = 0일 때 작동함 (∵ 저렴하기 때문)

○ (참고) 위와 같이 reset'으로 제공하는 것을 active low operation이라고 함

⑥ 비동기 입력 master/slave D flip-flop의 출력 파형

Figure. 46. 비동기 입력 master/slave D flip-flop의 출력 파형

⑽ 종류 2-3. master/slave JK flip-flop

① master/slave JK flip-flop의 회로도

Figure. 47. master/slave JK flip-flop의 회로도

② master/slave JK flip-flop의 출력 파형

4. 레지스터(registers) [목차]

⑵ flip-flop이나 latch들을 병렬로 연결하여 구성된 기억소자(주로 flip-flop)

① 메모리 중에서 속도가 가장 빠름

레지스터 > 캐시 > 연관 > RAM > ROM > 자기 코어 > 자기 디스크 > 자기 테이프

② 워드를 구성하는 비트 개수만큼의 flip-flop으로 구성되며, 여러 개의 flip-flop은 공통 clock의 입력에 의해 동시에 여러 비트의 자료가 저장된다.

③ 레지스터를 초기화하기 위해 저장값을 0으로 하는 것을 설정해제(CLR)라 한다.

⑵ 예시 1. universal shift register

① 정의 : 데이터를 이동시키는 데 사용하는 레지스터

② 종류 : PIPO(parallel-in to parallel-out), SISO(serial-in to serial-out), SIPO(serial-in to parallel-out)

③ 예시 : TTL 74194, 74HC165, 74HC595

④ 응용 1. 데이터 통신

⑤ 응용 2. time delay circuit

⑥ 응용 3. 디지털 금고 : 비밀번호를 순차적으로 눌러야 1에 해당하는 데이터가 전달되어 금고가 열림

⑶ 예시 2. n-bit up-counter

Figure. 49. 4-bit up-counter

① D와 QD는 MSB, A와 QA는 LSB이다.

② EN : EN = 1이면 출력은 갱신되고, EN = 0이면 출력값은 같은 값을 유지한다.

③ CLK : 위 그림은 rising edge triggered인 CLK pulse를 제공한다는 의미

○ 만약 falling edge triggered인 CLK pulse를 제공하면 down-counter를 구현할 수 있음

④ CLR : CLR = 1일 때, 다음 clock edge에서 state = 0이 된다.

⑤ LOAD : LOAD = 1일 때, 다음 clock edge에서 A, B, C, D 값으로 state가 갱신됨

⑥ CNT : 기본적으로 매 clock edge마다 state가 1씩 증가하고 출력은 곧 state임

○ CNT 단자가 없는 경우, CLR = LOAD = 0인 경우 CNT = 1인 것으로 간주

⑦ RCO : state가 1111일 때 1을 출력함

⑧ 종류 1. synchronous counter : 모든 출력단자의 신호가 동시에 바뀜

Figure. 50. 3-bit synchronous up-counter

Figure. 51. 3-bit synchronous up-counter의 출력파형

○ positive-edge triggering FF를 negative-edge triggering FF로 바꾼다고 하여 down-counter가 되지 않음

○ down-counter로 바꾸는 방법

○ FF1의 J1, K1에 들어가는 부분을 Q0'으로 바꿈

○ FF2의 J2, K2에 들어가는 부분을 Q0'·Q1'으로 바꿈

⑨ 종류 2. asynchronous counter : CLK과 먼 플립플롭은 가까운 플립플롭보다 약간 느리게 신호가 바뀜

Figure. 52. 3-bit asynchronous up-counter

Figure. 53. 3-bit asynchronous up-counter의 출력파형

○ negative-edge triggering FF를 positive-edge triggering FF로 바꾸면 down-counter가 됨

○ 예 : 74LS93A

⑩ 종류 3. up/down counter

Figure. 55. 3-bit up/down synchronous counter

대칭성을 이용하여 회로를 구성했음

⑪ 종류 4. cascaded counter : 예를 들어, modulus-32 counter는 modulus-4 counter와 modulus-8 counter로 만들 수 있음

⑷ register-to-register transfer : tri-state buffer (register)를 이용하여 data bus에 data를 전달함

① load data : IE는 input enable의 약자

② hold data : high Z-state를 이용함. IE는 input enable의 약자

③ transfer data : OE는 output enable의 약자

④ disconnect output line : OE는 output enable의 약자

⑤ clear : 비동기적으로 FF 레지스터를 초기화시킴

⑸ register file

① register file 기본 구조 : registers + MUX/DeMUX

○ DeMUX는 값을 저장시킬 register를 선택해 clock 신호를 생성한다.

○ WriteData는 실제 load시킬 데이터를 보낸다.

○ MUX는 읽어들일 register를 선택한다.

○ ReadData는 MUX에서 읽어들인 데이터이다.

Figure. 57. register file의 구조도

② CPU 구조도 : register file은 CPU의 핵심 요소

Figure. 58. 단일 사이클 데이터패스(single cycle datapath)의 구조도

○ 요소 1. 프로그램 카운터, 프로그램 계수기(PC, program counter)

○ 다음 번에 실행할 명령어의 번지를 기억하는 레지스터

○ 분기 명령이 실행되는 경우 그 목적지로 갱신

○ 요소 2. 명령 레지스터(IR, instruction register) : 현재 실행 중인 명령의 내용을 기억하는 레지스터

○ 요소 3. 누산기(AC, accumulator) : 연산된 결과를 일시적으로 저장하는 레지스터. 연산의 중심

○ 요소 4. 상태 레지스터(status register), PSWR(program status word register), 또는 플래그 레지스터

○ PSW은 시스템의 순간순간의 상태를 기록해 온 정보를 지칭

○ 오버플로, 언더플로, 자리올림, 계산상태, 인터럽트 등을 처리. 프로그램 제어와 밀접한 연관

○ 요소 5. 메모리 주소 레지스터(MAR, memory address register)

○ 기억장치를 출입하는 데이터 주소를 기억하는 레지스터

○ 요소 6. 메모리 버퍼 레지스터(MBR, memory buffer register)

○ 기억장치를 출입하는 데이터가 잠시 기억되는 레지스터

○ CPU와 기억장치의 연산 속도 차이로 인해 꼭 필요

○ 요소 7. 베이스 레지스터(base register) : 명령이 시작되는 시작 번지를 기억하고 있는 레지스터

○ 요소 8. 인덱스 레지스터(index register)

○ 주소 변경시 쓰거나 반복 연산의 횟수를 세는 레지스터

○ 프로그래머가 내용을 변경할 수 있음

○ 요소 9. 데이터 레지스터(data register) : 연산에 사용될 데이터를 기억하는 레지스터

○ 요소 10. 시프트 레지스터(shift register)

○ 저장된 값을 좌 또는 우로 1 bit씩 옮기는 레지스터

○ 2배 길이 레지스터라고도 함

○ 요소 11. 메이저 스테이트 레지스터(major state register)

○ CPU의 메이저 상태(인출, 간접, 실행, 인터럽트)를 저장하는 레지스터

③ intel CPU의 구조도

5. ROM(read-only memory) [목차]

# ROM과 관련된 내용은 Implementation Technology에서 정리했음

# 이유 : 조합논리의 성격이 강하기 때문

6. RAM(random access memory) [목차]

⑴ RAM : RWM(read/write memory)라고도 함

① 정의 : 자유롭게 읽고 쓸 수 있는 기억장치

② RAM에는 현재 사용중인 프로그램이나 데이터가 저장

③ 전원이 꺼지면 기억된 내용이 모두 사라지는 휘발성(volatile) 메모리

④ 일반적으로 '주기억 장치' 또는 '메모리' 하면 램을 의미

⑵ SRAM(static random acess memory) : cache, large register file

① SRAM의 기본 property : 출력을 증폭하기 위해 BL, BL'을 모두 이용

② 예시 : 1024 × 4-bit SRAM. DRAM도 비슷함

Figure. 61. internal block diagram

○ I/O

○ CS : clock signal○ WE : 읽기/쓰기 모드. WE'이 0이 되면 read에서 write로 바뀐다.

○ 10개의 select로 구성돼 있음 : 210 addresses(words)

○ 1st. 6개의 select의 조합이 한 개의 16 × 4 bits row를 선택. 이 decoder를 row decoder라고 한다.

○ 2nd. 나머지 4개의 select 조합이 각 16-bit 데이터를 1-bit로 골라냄

○ 3rd. 이 과정에서 sense amplifier가 데이터를 증폭시킴 (DRAM의 경우)

○ 4th. 각 storage matrix로부터 온 1-bit 데이터를 그대로 Data Buffers로 전달

③ timing constraints

○ memory access time : 주소에서 출력이 나올 때까지의 시간

○ memory cycle time : 신호를 보낸 후 다시 신호를 보낼 수 있을 때까지의 시간 간격

○ memory access time ≤ memory cycle time

○ memory access를 한 뒤 다른 clock cycle에서 값을 받으면 신호 제어가 불가능

⑶ DRAM(dynamic random access memory) : main memory, large cache

① 기본 property

② DRAM의 원리

○ 1st. 만약 Cc > CBL(0.5Vdd)이면 cell의 switch on 시 나중 전위는 0.5Vdd + δ

○ 1*st. 만약 Cc < CBL(0.5Vdd)이면 cell의 switch on 시 나중 전위는 0.5Vdd - δ

○ 2nd. sense amplifier가 이 δ를 증폭시킨다.

○ sense amplifier : 2 pMOS, 2 nMOS로 이루어져 있다.

○ 3rd. read를 하고 난 뒤 Cc와 CBL을 원 상태로 충전시킨다.

○ 4th. Cc의 회로를 차단한 뒤 CBL을 0.5Vdd로 맞춘다.

③ DRAM의 문제점

○ 작은 신호, read operation이 기억 내용에 영향을 미침

○ DRAM의 내용은 시간이 지날수록 기억 내용이 손상됨

④ DRAM scaling limit

Figure. 65. DRAM의 현미경 사진

⑷ DRAM과 SRAM의 비교

| . | 정적 램(SRAM) | 동적 램(DRAM) |

| 메커니즘 | latch를 두 개의 스위치로 연결한 것 (flip-flop 기반) |

커패시터의 충전 및 방전 (콘덴서 기반) |

| capacity | 16K bits (집적도 낮음) |

64K bits (집적도 높음) |

| access time | < 50 ns (접근 속도 빠름) |

< 100 ns (접근 속도 느림) |

| write time | < 50 ns | < 100 ns |

| power supply | < 5.0 V | < 5.0 V |

| active power | 625 mW (전력 소모 많음) |

300 mW (전력 소모 적음) |

| erase time | no need | no need |

| # of RD/WT | R&W infinite (> 1015) | R&W infinite (> 1015) |

| data retention time | no refresh | need refresh. volatile |

| operation current | ~ 100 mA | ~ 100 mA |

| standby current | ~ 10 μA | ~ 200 μA |

| density | small | medium / large |

| cost per unit | 250 milicents | 45 milicents |

| usage | Cache memory | Main memory |

Table. 2. DRAM과 SRAM의 비교

⑸ 차세대 메모리

① PRAM(phase-change RAM) (ref)

○ PRAM 또는 PCM은 전원이 꺼져도 저장된 정보가 지워지지 않으면서 DRAM 만큼의 빠른 속도를 지원

○ 게르마늄 안티몬 텔룰라이드라는 물질이 전류의 온도에 따라 비결정(액체)/결정(고체) 상태가 전환

○ 결정 상태일 때는 0, 비결정 상태일 때는 1을 지정

Figure. 66. PCM의 구조도

Figure. 67. PCM의 memory cell의 결정화도에 따른 저항변화

② FRAM : 강유전체에 전극을 가해 반대 성질을 갖도록 함으로써 메모리 반도체로 이용하는 방식

③ MRAM : 강자성 물질의 N극과 S극의 성질을 이용해 데이터를 저장하는 방식

7. 플래시 메모리(flash memory) [목차]

⑴ 개요

① 정의 : EEPROM의 일종으로 전기적 성질을 이용하여 반도체 소자에 기록된 정보를 읽음

② 한 셀은 single floating gate MOS transistor로 구성됨

⑵ 원리

① memory cell의 구성

Figure. 68. (참고) MOS-FET의 구조. 증가형 MOS-FET

Figure. 69. flash memory cell의 구성

○ Floating gate에 전자가 채워져 있는 경우

○ Control gate에 (+) 전압을 인가해도 전자가 상쇄하여 MOS-FET이 도통되지 않음

○ Source 단자는 접지와 연결돼 있으므로 Source와 연결된 출력이 LOW가 됨

○ Floating gate에 전자가 없는 경우

○ Control gate에 (+) 전압을 인가하면 MOS-FET이 도통됨

○ Source 단자는 (+) 전압과 연결된 Drain으로 인해 Source와 연결된 출력이 HIGH가 됨

② write operation(programming operation)

Figure. 70. flash memory의 write operation

③ read operation

Figure. 71. flash memory의 read operation

④ erase operation

Figure. 72. flash memory의 erase operation

⑤ basic flash memory array

Figure. 73. basic flash memory array

⑶ 장점

① 소비 전력이 적음

② high density Read/Write memory

③ 전원이 차단되더라도 저장 정보가 사라지지 않음 (비휘발성)

④ 정보의 입출력이 자유로움

⑷ 종류

① 데이터 저장형 (직렬구조)

○ 해당 블록으로 이동 후 직렬로 연결된 각 셀을 순차적으로 접근함

○ 고집적이 가능하고 핸드 디스크를 대체할 수 있어 고집적 음성이나 화상 등의 저장용으라 많이 사용

○ 삼성전자가 세계 시장의 60% 이상을 점유함

② 코드 저장형 (병렬구조)

○ 순서에 관계없이 임의의 셀로 접근 가능

○ 속도가 빠름

○ 플레시 메모리 시장의 80%를 차지

○ 인텔, AMD 등이 주도함

⑸ 응용 : 휴대전화, MP3 플레이어, 개인용 정보 단말기, 디지털 카메라

8. 메모리 성능 비교 [목차]

| . | Speed | Power | Capacity | Noise Immunity | Cost |

| TTL | Fast | High | Low | Low | High |

| ECL | Fastest | Highest | Lowest | Lowest | Highest |

| NMOS | Midium | Low | Highest | High | Lowest |

| CMOS | Slowest | Lowest | Highest | Highest | Low |

Table. 3. 메모리로서의 성능 비교

⑴ TTL(transistor-transistor logic) : operating speed가 MOS 메모리보다 빠름

⑵ MOS 메모리

① 장점 : power consumption이 TTL보다 10배 더 적음

② 단점 : 정전기 방전으로 인한 손상 주의

9. 동기화(synchronization) [목차]

⑴ 시간 제한(timing constraints)

Figure. 74. clock의 setup time과 hold time

Figure. 75. clock의 timing constraints

① 펄스 폭(pulse width, tw) : 한 주기 동안 high 레벨을 유지하고 있는 시간

② 의무 사이클(duty cycle) : clock 값이 1이 되는 반복구간. 한 주기 동안 펄스 값의 비율

○ Dt = (tw / τ) × 100

③ setup time(Tsetup) : clock의 해당 edge 전에 input이 안정화되는 데 필요한 시간

④ hold time(Th) : clock의 해당 edge 후에 input이 안정화되는 데 필요한 시간

⑤ contamination delay

○ Tccq : Q가 불안정해지기 시작하는 시간

○ Tcd : D가 불안정해지기 시작하는 시간

⑥ propagation delay

○ Tpcq : Q가 다시 안정해지는 시간

○ Tpd : D가 다시 안정해지는 시간

⑦ setup time constraint : Tc > Tpcq + Tpd + Tsetup

⑧ hold time constraint : Th < Tccq + Tcd

⑨ 최대 클럭 주파수(maximum clock frequency) : 동작을 위한 최대 주파수

⑩ 시간 여유(time margin) : setup time margin, hold time margin으로 구분

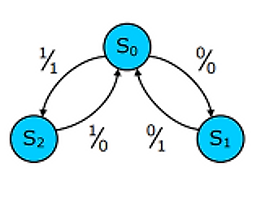

⑵ 동기화(synchronization)

① 동기적 회로 vs 비동기적 회로

○ 동기적 회로는 참조신호(clock)에 따라 입력, 상태, 출력이 바뀜

○ R-S latch 등의 비동기적 회로는 참조신호가 없어 glitch를 주의해야 함

② 비동기적 입력

○ 비동기적 입력은 순간적으로 값이 변하면서 잘못된 정보를 전달할 수 있음

○ reset 버튼 등과 같이 동기화 회로에서도 비동기적 입력은 반드시 필요함

③ 입력단자에 synchronizer를 달아서 비동기적 입력 문제를 해결할 수 있음

Figure. 76. 비동기적 입력을 동기화시키기 위한 synchronizer

⑶ 동기화 실패(synchronizer failure) (ref)

① asynchronous 입력이 synchronizer의 timing constraints가 위반된 경우

○ 예시

○ 일정 시간은 0도 1도 아닌 상태(meta-stable state)에 있게 된다.

Figure. 78. meta-stable state의 그래프와 해석

○ 출력값이 바뀌는 것은 공을 밀어서 반대편으로 옮기는 것과 유사하다.

○ 공을 옮기다가 중간에 멈추면 위에 대롱대롱 매달려 있는 것이다.

○ 이론적으로 meta-stable state가 가능하다.

○ 열불균형이나 입력 노이즈로 어느 한 상태로 가나 긴 시간이 필요할 수도 있다.

○ 즉, meta-stable state의 영향이 계속 남아 시스템 자체가 에러가 날 수 있다.

② 해결책

○ 해결책 1 : clock 주기를 연장하는 방법

○ stable state가 되도록 기다려 주는 방법

○ 고속처리가 중요한 회로는 clock 주기가 짧아야 하기 때문에 적합치 않다.

○ 해결책 2 : fast logic technology를 써서 데이터가 빠르게 stable하게 하는 방법

○ 해결책 3 : multistage synchronizer

○ synchronized meta-stable input을 F/F로 synchronized stable input으로 전환

Figure. 79. multistage synchronizer의 예시

③ clock domain crossing

○ 서로 다른 clock 도메인 간의 신호 전달은 asynchronous 입력 상황과 유사하다.

○ clock 도메인을 변경시키고, meta-stable을 막기 위해 2 synchronizers가 필요

⑷ clock skew

① 정의 : Gate 간의 delay로 인해 나중 가서 신호가 동기화되지 않는 현상

② 해결책 : 중간 중간에 filp-flop를 삽입하여 clock 신호에 맞게 동기화시킴

Figure. 80. clock skew를 해결하는 방법 예시

입력: 2016.11.20 20:14

수정: 2020.05.18 10:50

'▶ 자연과학 > ▷ 논리설계' 카테고리의 다른 글

| 【논리설계】 9강. 프로토콜 (0) | 2016.11.22 |

|---|---|

| 【논리설계】 8강. 순차논리 (0) | 2016.11.08 |

| 【Logic Design】 adder circuits (0) | 2016.10.10 |

| 【논리설계】 6강. Implementation Technology (3) | 2016.09.28 |

| 【논리설계】 5강. 하드웨어 기술 언어(Verilog) (0) | 2016.09.28 |

최근댓글