9강. 프로토콜(protocol)

추천글 : 【논리설계】 논리설계 목차

1. 프로토콜 [본문]

2. Keyboard [본문]

3. KeyboardDecode [본문]

4. Sender [본문]

5. Receiver [본문]

6. DisplayControl [본문]

7. Display [본문]

1. 프로토콜 [목차]

⑴ 예 : RS-232 serial line protocol, RS-485

① (참고) RS-485는 8 bit 단위이며 RS-232의 상위 호환 버전

⑵ 공중 전화 교환망(PSTN)을 통한 단말장치(DTE)/모뎀(DCE) 접속 규격이다. V.24, V.28, ISO2110을 사용하는 접속 규격과 기능적으로 호환성을 가지며, 현재 가장 많이 사용된다.

⑶ 25핀으로 구성된 커넥터로, 전송 거리는 15m 이하이다.

⑷ 데이터 신호 속도는 최고 20Kbps이다.

⑸ 전이중/반이중, 동기/비동기 모두에 대응한다.

⑹ 주요 핀의 기능

| 핀 번호 | 핀 이름 | 기능 | |

| 1 | FG(Frame Ground) GND(Ground) |

보호용 접지 회로 | |

| 2 | TXD(Transmitted Data) | 송신 데이터. 데이터를 송신하는 기능 | |

| 3 | RXD(Receivered Data) | 수신 데이터. 데이터를 수신하는 기능 | |

| 4 | RTS(Return To Send) | 송신 요청. DTE에서 DCE한테 송신을 요청하는 기능 | |

| 5 | CTS(Clear To Send) | 송신 준비 완료. DCE에서 DTE한테 송신 준비 완료를 알리는 기능 | |

| 6 | DSR(Data Set Ready) | DCE 정상 상태. DCE의 동작 상태를 알리는 기능 (ON: 동작, OFF: 동작 안 함) |

|

| 7 | SG(Signal Ground) | 신호 접지. 모든 신호의 기준 전압으로 되어 있음 | |

| 8 | DCD(Data Carrier Detect) | 수신선 신호 감지. DCE가 선로 쪽으로부터 감지할 수 있는 신호를 수신하고 있음을 DTE에 알리는 기능 | |

| 20 | DTR(Data Terminal Ready) | DTE 정상 상태. DTE가 정상 동작을 하고 있음을 DCE에 알리는 기능 | |

| 22 | RI(Ring Indicator) | 링 감지 신호. 상대편으로부터 링 신호가 들어오고 있다는 것을 DTE 에 알리는 기능 | |

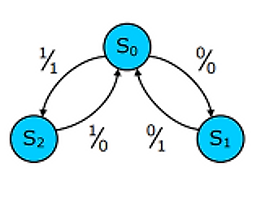

Figure. 1. 단일 시리얼 선으로 연결된 sender/receiver에 대한 도식

2. Keyboard [목차]

Figure. 2. 디바운싱 회로가 포함된 Keyboard 블록의 도식

Figure. 3. 단일 키보드 키에 대한 도식

⑴ Key 누름 → 스위치 연결 → Keypad, Common(Gnd) 출력 → X, Y = 1

⑵ Key 뗌 → 스위치 개방 → Keypad, HIGH 출력 → X, Y = 0

⑶ 여러 Key에 대해 X, Y가 결정되므로, 실제로는 Keypad 출력단자에 OR gate가 존재

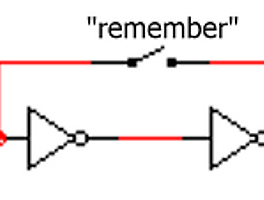

⑷ 디바운싱 회로 : 기계적 스위치의 한 번에 붙지 않는 문제(바운싱)를 해결하는 회로 (ref)

① RC 적분회로, RS_FF 등이 대표적

3. KeyboardDecode [목차]

Figure. 4. KeyboardDecode와 Sender 간의 상호작용(handshake)

⑴ Send : Sender로 정보를 보내겠다는 표시로 Acks 신호를 받으면 0이 된다.

⑵ CharToSend : 읽어들인 7개의 입력이 8 bits ASCII 코드로 번역된 값

⑶ AckS(acknowledge) : Sender가 성공적으로 정보를 받고 처리 시 출력하는 표시

⑷ 전체 코드

`timescale 1ns / 1ps

module KeyboardDecode(

input ClkS, input ResetS, input R1, input R2,

input R3, input R4, input C1, input C2,

input C3, input AckS, output Send, output [7:0] CharToSend

);

reg [7:0] CharToSend;

reg Send;

wire KeyPress;

assign KeyPress = (R1 || R2 || R3 || R4) && (C1 || C2 || C3);

always@(posedge ClkS) begin

if(ResetS) Send <= 0;

else begin

if(AckS) Send <= 1;

else if(KeyPress && !AckS) begin

if(R1 && C1) CharToSend <= 8'b00110001; // '1'

else if(R1 && C2) CharToSend <= 8'b00110001; // '2'

else if(R1 && C3) CharToSend <= 8'b00110001; // '3'

else if(R2 && C1) CharToSend <= 8'b00110001; // '4'

else if(R2 && C2) CharToSend <= 8'b00110001; // '5'

else if(R2 && C3) CharToSend <= 8'b00110001; // '6'

else if(R3 && C1) CharToSend <= 8'b00110001; // '7'

else if(R3 && C2) CharToSend <= 8'b00110001; // '8'

else if(R3 && C3) CharToSend <= 8'b00110001; // '9'

else if(R4 && C1) CharToSend <= 8'b00110001; // '*'

else if(R4 && C2) CharToSend <= 8'b00110001; // '0'

else if(R4 && C3) CharToSend <= 8'b00110001; // '#'

Send <= 1;

end

end

end

endmodule

4. Sender [목차]

Figure. 5. Sender의 데이터 경로

⑴ Send : KeyboardDecode로부터 데이터를 받겠다는 표시

⑵ CharToSend : KeyboardDecode로부터 받은 8 bits 데이터

⑶ AckS : Sender가 성공적으로 받은 데이터를 처리중이라는 표시로 waiting signal의 일종

⑷ TxD : 개시 비트(0) - 8 bits 데이터 - 종결 비트(1)순으로 1 bit씩 전달

① 8 bits 데이터는 MSB에서 LSB 순으로 전달

⑸ 전체 코드

`timescale 1ns / 1ps

module Sender(

input ClkS, input ResetS, input Send,

input [7:0] CharToSend,

output AckS, output TxD

);

reg TxD;

reg [7:0] CharToSend;

reg [3:0] bitCounter; // keeps count of which bit is being sent

reg go;

always @(posedge ClkS) begin

if(ResetS) begin

TxD <= 1; go <= 0;

end

else begin

if(send) begin // loading characters sent from KeyboardDecoder

CharToSend <= CharToSend; // red CharToSend <= wire CharToSend

bitCounter <= 0; go <= 1;

end

else begin // allocating TxD with proper value with the condition "go = 1"

bitCounter <= bitCounter + 1;

if(go) begin

if(bitCounter == 0) TxD <= 0; // Start bit

else if(bitCounter > 0 && bitCounter <= 8)

TxD <= CharToSend[8 - bitCounter];

else if(bitCounter > 8) begin

TxD <= 1;

go <= 0;

end

end

end

end

end

assign AckS = go;

endmodule

5. Receiver [목차]

Figure. 6. Receiver와 DisplayControl과의 상호작용(handshake)

⑴ RxD : Sender로부터 1 bit씩 정보가 전달되는 선

⑵ Rcvd : Receiver가 Sender로부터 정보를 모두 받았다는 표시

① Rcvd = 1이면(처리하지 못한 데이터가 있으면) RxD를 무시한다.

⑶ CharRcvd : Receiver가 Sender로부터 받은 8 bits 데이터

⑷ AckR : DisplayControl이 Receiver로부터 성공적으로 정보를 받고 처리 시 출력하는 표시

⑸ Receiver와 Sender 간 Ack 신호가 없어서 문제가 야기될 수 있다.

① Sender와 Receiver 간 거리가 멀어 신호도달 시간이 길다.

② race condition : Receiver가 Sender 신호를 중간부터 받는 현상

③ 해결책 : buffer를 마련해 Sender의 신호를 10개 정도 미리 저장해 둔다.

⑹ oversampling : Receiver의 clock 진동수는 Sender의 정수배(≥ 2)이다. (ref)

① aliasing : 원본 신호 주파수 이하의 주파수로 샘플링 될 시 고주파 영역이 손상되는 현상

○ 예 : 빠른 프로펠러가 눈으로 보기에 느리게 회전하는 것처럼 보이는 현상

○ FFT(fast Fourier transform), Nyquist theorem

Figure. 7. Receiver와 Sender의 clock 진동수가 같을 때의 문제점

② 정수배인 이유

Figure. 8. clock 간 동기화에 따른 샘플링 차이

⑺ 전체 코드

`timescale 1ns / 1ps

module Receiver(

input ClkR, input ResetR, input RxD, input AckR,

output [7:0] CharRcvd, output Rcvd

);

reg [4:0] bitCounter; // keep count of number of bits through RxD (0 ~ 15)

reg [1:0] cycleCounter; // for oversampling

reg [8:0] characterReceived;

reg go; // flag indicating a character is arriving

always @(posedge ClkR) begin

if(ResetR) begin go <= 0; Rcvd <= 0; end

else begin

if(!go && !Rcvd && !AckR && RxD);

if(!go && !Rcvd && !AckR && !RxD) begin

go <= 1;

bitCounter <= 0;

cycleCounter <= 0;

end

if(go) begin

if(cycleCounter == 0) begin

characterReceived[8 - bitCounter] <= RxD;

if(bitCounter < 8) bitCounter <= bitCounter + 1;

else begin // the entire characters have been received

go <= 0;

Rcvd <= 1;

end

end

end

if(AckR) Rcvd <= 0; // DisplayControl is still not available

end

end

assign CharRcvd[7:0] = characterReceived[7:0];

endmodule

6. DisplayControl [목차]

⑴ Rcvd : Receiver가 데이터를 보낼 준비가 됐다는 신호

⑵ CharRcvd : Receiver가 보내는 데이터

⑶ AckR : DisplayControl가 성공적으로 받은 데이터를 처리중이라는 신호로 wating signal의 일종

⑷ RS : reset의 약자

⑸ DB : data bus의 약자

⑹ E : enable의 약자

⑺ 전체 코드

`timescale 1ns / 1ps

module DisplayControl(

input ClkR, input ResetR, input Rcvd, input [7:0] CharRcvd,

output AckR, output [7:0] DB, output RS, output Enable

);

reg [7:0] databus;

reg Enable;

reg RS;

reg AckR;

reg initMode; // indicates wheter the initialize sequence is in progress

reg [4:0] initState; // states for initialization sequence

parameter start = 0;

parameter step1 = 1;

parameter endstep1 = 2;

parameter step2 = 3;

parameter endstep2 = 4;

parameter step3 = 5;

parameter endstep3 = 6;

parameter step4 = 7;

parameter endstep4 = 8;

parameter final = 9;

assign DB = (initMode)? databus : CharRcvD;

always @(posedge ClkR) begin

if(ResetR) begin

initMode <= 1;

initState <= start;

Enable <= 0;

AckR <= 0;

end

else if(initMode) begin // do initialize

case(initState)

start: begin RS <= 0; initState <= step1; end

step1: begin Enable <= 1; databus <= 8'b00000001; initState <= endstep1; end

endstep1: begin Enable <= 0; initState <= step2; end

step2: begin Enable <= 1; databus <= 8'b00110011; initState <= endstep2; end

endstep2: begin Enable <= 0; initState <= step3; end

step3: begin Enable <= 1; databus <= 8'b00001100; initState <= endstep3; end

endstep3: begin Enable <= 0; initState <= step4; end

step4: begin Enable <= 1; databus <= 8'b00000110; initState <= endstep4; end

endstep4: begin Enable <= 0; initState <= final; end

final: begin RS <= 1; initMode <= 0; initState <= final; end

endcase

end

else begin

if(Rcvd && !AckR) begin // handshake with DisplayControl and Display

case(Enable) // Enable should be HIGH to implement properly

0: begin Enable <= 1; end

1: begin Enable <= 0; AckR <= 1; end

endcase

end

else begin // complete handshake lowering AckR after Rcvd is lowered

if(!Rcvd) AckR <= 0;

end

end

end

endmodule

7. Display [목차]

Figure. 9. LCD screen operations

Figure. 10. Timing of LCD screen interface

입력: 2016.11.27 01:54

'▶ 자연과학 > ▷ 논리설계' 카테고리의 다른 글

| 【논리설계】 응용 : 곱셈기 (0) | 2016.11.27 |

|---|---|

| 【논리설계】 응용 : 덧셈기 (0) | 2016.11.27 |

| 【논리설계】 8강. 순차논리 (0) | 2016.11.08 |

| 【논리설계】 7강. 클럭과 메모리 (0) | 2016.10.26 |

| 【Logic Design】 adder circuits (0) | 2016.10.10 |

최근댓글