9강. 반도체 증폭회로

추천글 : 【회로이론】 회로이론 목차

1. 바이어스 회로 [목차]

⑴ 문제점 : 증폭회로의 입력신호는 교류이고 크기가 작음

⑵ 트랜지스터가 의도된 기능을 수행하도록 적절한 직류 전압을 걸어줌

① 일반적으로 BJT 트렌지스터의 경우 활성 영역에서 기능을 설계함

② 일반적으로 FET 트렌지스터의 경우 포화 영역에서 기능을 설계함

⑶ BJT 트랜지스터의 바이어스 회로

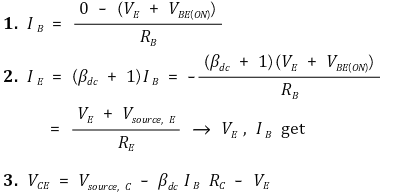

① 베이스 바이어스 회로

○ 단일 전원과 저항 2개로 VC와 VB를 조절하는 회로

○ 온도에 대한 안정성이 낮아서 잘 사용하지 않음

Figure. 1. 베이스 바이어스 회로

② 이미터 바이어스 회로

○ 전압원 2개로 VC와 VB를 조절

○ 전압원이 두 개나 필요하다는 사실 자체가 단점

Figure. 2. 이미터 바이어스 회로

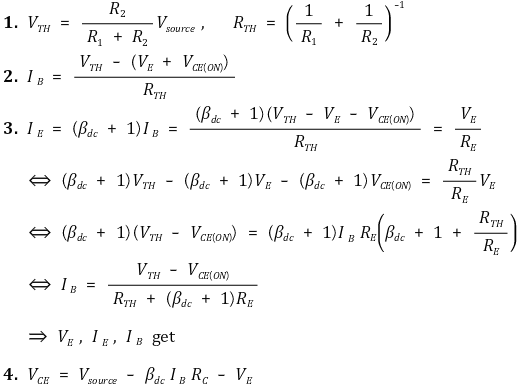

③ 전압 분배 바이어스 회로

○ Vsource를 분할하여 VB에 적절한 전압을 공급

Figure. 3. 전압 분배 바이어스 회로

○ 테브낭 등가회로

Figure. 4. 전압 분배 바이어스 회로 등가회로

RTH 아래에 있는 전원은 테브낭 등가전원임

④ 실무적인 조언

○ 일반적으로 VCE는 0.5VCC로 설정

○ 일반적으로 VE는 0.1VCC로 설정

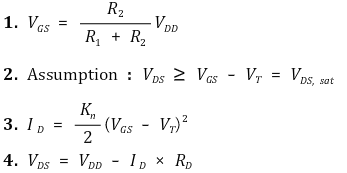

⑷ FET 트렌지스터의 바이어스 회로

① 전압 분배 바이어스 회로

Figure. 5. FET 트렌지스터의 전압 분배 바이어스 회로

2. 대신호, 소신호 해석 [목차]

⑴ 일반적인 회로 설계

① 직류 전압은 바이어스를 위해 꼭 필요함

② 직류 전압으로 인해 출력 신호에 왜곡이 발생하지 않도록 커패시터를 사용 : 직류에 대한 차단효과

③ 커패시턴스가 충분히 큰 커패시터를 사용하여 교

류신호는 쉽게 통과하도록 함 : 교류에 대한 도통효과

⑵ 신호 해석

① 소신호 해석 : 직류 전원과 교류 전원을 분리하여 중첩의 원리로 회로를 해석하는 것

○ 일반적으로 직류 제어량은 대문자로, 교류 제어량은 소문자로 표시

② 대신호 해석 : 직류 전원과 교류 전원을 함께 고려하여 시간 도메인으로 해석하는 것

③ 대신호 해석은 수학적으로 굉장히 복잡하므로 소신호 해석이 선호됨

3. BJT 트랜지스터를 이용한 증폭기 [목차]

⑴ 교류 등가 회로

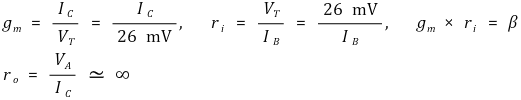

① 모델 1. 하이브리드 π 모델

Figure. 6. 하이브리드 π 모델

○ gm, ri를 계산할 때는 직류해석을 통해 얻은 제어량(전류, 전압)을 이용함

○ 이유 : 교류 소신호는 회로의 제어량을 크게 변경시키지 않으므로

○ 이미터라고 표시된 부분이 접지이고 이미터와 접지 사이에 저항이 있는 경우에도 gm vbe가 유지됨

② 모델 2. common emitter re 모델

Figure. 7. re 모델

○ β × re를 계산할 때는 직류해석을 통해 얻은 제어량(전류, 전압)을 이용함

○ 이유 : 교류 소신호는 회로의 제어량을 크게 변경시키지 않으므로

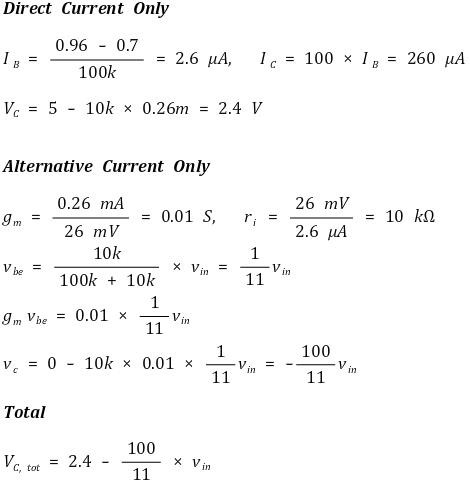

⑵ 공통 이미터 회로

Figure. 8. 공통 이미터 회로 예제

① 정의 : 베이스 단자에 입력, 컬렉터 단자에 출력이 연결된 회로

② 직류 Vcc에 의해 동작 영역 결정

③ 교류입력 Vin을 증폭하여 Vout으로 출력 : 위상은 반전됨

⑶ 공통 베이스 회로

① 정의 : 이미터 단자에 입력, 컬렉터 단자에 출력이 연결된 회로

⑷ 공통 컬렉터 회로

① 정의 : 베이스 단자에 입력, 이미터 단자에 출력이 연결된 회로

4. FET 트랜지스터를 이용한 증폭기 [목차]

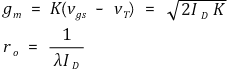

⑴ 교류 등가 회로

Figure. 9. FET 트랜지스터 교류 등가 회로

① λ는 소자 고유값이며 해석의 편의를 위해 0으로 곧잘 가정함 → ro = ∞

② gm을 계산할 때는 직류해석을 통해 얻은 제어량(전류, 전압)을 이용함

③ 이유 : 교류 소신호는 회로의 제어량을 크게 변경시키지 않으므로

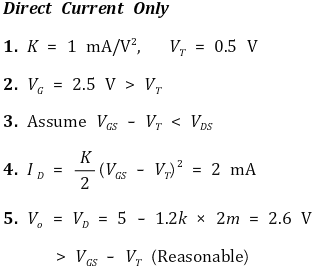

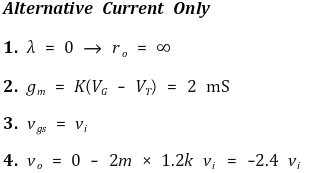

⑵ 공통 소스 회로

Figure. 10. 공통 소스 회로

① 정의 : 게이트 단자에 입력, 드레인 단자에 출력이 연결된 회로

② 직류 해석 : 커패시터 부분은 잘린 전선으로 간주. 직류 Vcc에 의해 동작 영역 결정

③ 교류 해석 : 교류 입력 소신호 Vs에 의해 Vo가 변함

Figure. 11. 공통 소스 회로 교류 등가 회로

⑶ 공통 게이트 회로

① 정의 : 소스 단자에 입력, 드레인 단자에 출력이 연결된 회로

⑷ 공통 드레인 회로

Figure. 12. 공통 드레인 회로

① 정의 : 게이트 단자에 입력, 소스 단자에 출력이 연결된 회로

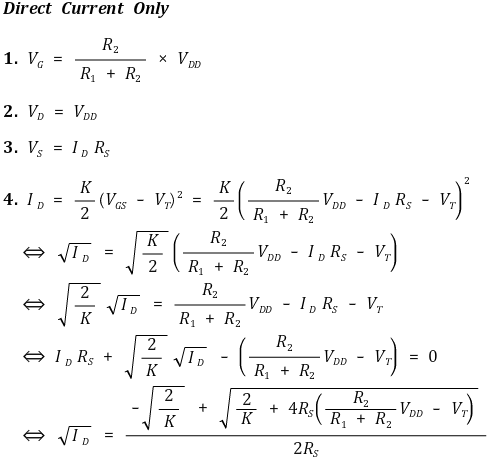

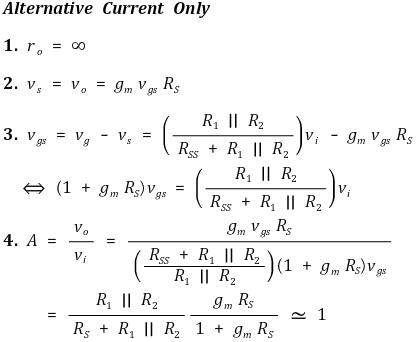

② 직류 해석

③ 교류 해석

Figure. 13. 공통 드레인 회로 교류 등가회로

④ 결론

○ 입력 신호 자체는 유지하면서 물린 저항이 작아진 것과 같은 효과

○ 교류 전압원의 내부 저항이 굉장히 큰 경우 사용

○ source follower 참고

입력: 2019.12.04 00:01

'▶ 자연과학 > ▷ 회로이론' 카테고리의 다른 글

| 【회로이론】 7-1강. 다이오드 실험 (0) | 2019.11.28 |

|---|---|

| 【회로이론】 10강. Op Amp (2) | 2019.11.25 |

| 【회로이론】 8강. 트랜지스터 (1) | 2019.11.08 |

| 【회로이론】 7강. 다이오드 (1) | 2019.11.08 |

| 【회로이론】 5-3강. 함수 생성기(function generator) 사용법 (0) | 2016.09.24 |

최근댓글