8강. 트랜지스터(transistor)

추천글 : 【회로이론】 회로이론 목차

a. 트랜지스터 실험

b. 반도체 관련 문제

1. 트랜지스터(transistor) [목차]

⑴ 개요

① 트랜스(trans)와 저항(resistor)의 합성어

② 최초의 트랜지스터 특허 : J. E. Lilienfeld (1926)

③ 기능 : 신호 증폭 기능, 스위칭 기능

④ 구성 1. emitter, source : 물이 들어오는 상수도에 비유할 수 있음

⑤ 구성 2. base, gate : 수도꼭지에 비유할 수 있음

⑥ 구성 3. collector, drain : 물이 나오는 곳으로 비유할 수 있음

⑵ 종류 1. 쌍극형 접합 트랜지스터 : TTL 메모리를 구성함

① n형 반도체와 p형 반도체를 접합하여 제조

② 전류로 전류를 제어

③ 쌍극성

⑶ 종류 2. 전계효과형 트랜지스터 : MOS 메모리를 구성함

① 도체, 부도체, 반도체를 결합하여 제조

② 전압으로 전류를 제어

③ 단극성

2. 쌍극형 접합 트랜지스터(BJT, bipolar junction transistor) [목차]

⑴ 개요

① 정의 : n형 반도체와 p형 반도체를 접합하여 제조

② 최초의 이론 정립 : Bardeen, Brattain, Shockley

③ 최초의 실험적 규명 : Gordon Teal

⑵ 구조

① NPN 트랜지스터와 PNP 트랜지스터가 있음

○ 일반적으로 NPN 트랜지스터를 기준으로 생각

○ PNP 트랜지스터는 NPN 트랜지스터에서 인가전압을 뒤집으면 정확히 동일

② BJT 트랜지스터는 베이스, 이미터, 컬렉터로 구성

○ 이미터 : 전하 운반자를 방출하는 부분이라는 의미

○ 컬렉터 : 전하 운반자를 받아들이는 부분이라는 의미

○ 이미터의 도핑 농도가 컬렉터의 도핑 농도보다 높음

○ 베이스는 도핑이 덜 돼 있음

③ 전하는 이미터(E, emitter) → 베이스(B, base) → 컬렉터(C, collector)로 전하가 이동

Figure. 1. NPN 트랜지스터(왼쪽)과 PNP 트랜지스터(오른쪽)의 기호

○ B-E 접합, B-C 접합은 다이오드로 볼 수 있음

○ NPN 트랜지스터 기호 : 전자가 이미터 → 베이스 → 컬렉터로 이동. 전류는 반대 방향

○ PNP 트랜지스터 기호 : 정공이 이미터 → 베이스 → 컬렉터로 이동. 전류는 같은 방향

⑶ 영역 1. 순방향 능동영역(활성영역, active region)

① 조건 (NPN 트랜지스터 기준)

○ B-E 접합은 순방향 바이어스

○ B-C 접합은 역방향 바이어스

○ 즉, VE < VB < VC일 것

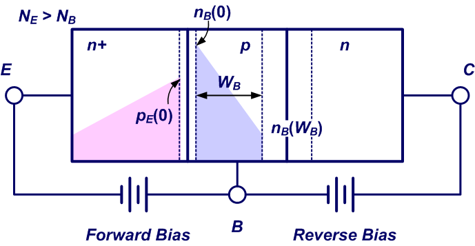

② 메커니즘

Figure. 2. 활성영역 NPN 트랜지스터의 작동 원리

(붉은 점은 전자를 표시)

○ 1st. E-B에 인가된 순방향 바이어스는 전자를 이미터에서 베이스로 이동시키며 IE를 형성

○ 2nd. 베이스는 도핑이 덜 돼 있고, 그 폭은 일반적으로 10-6 m : IE를 형성하는 전자 중 5% 미만이 양공과 결합

○ 3rd. 나머지 95%의 전자는 베이스에서 컬렉터로 이동하며 IC를 형성

○ 4th. 대부분의 전류가 컬렉터로 흐름 : 컬렉터 전류는 베이스로 들어온 전하의 영향이 큼. 전기장의 영향 작음

○ 5th. 위와 같은 방식으로 BJT 트랜지스터에서 확산전류가 발생 : 전계에 의한 전류인 드리프트 전류가 아님

○ 다음 방정식이 성립함은 명백함

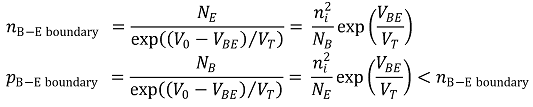

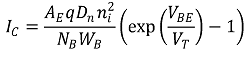

③ 수식화

Figure. 3. 트랜지스터의 B-E 접합 해석

○ B-E 접합 : 다이오드로 볼 수 있음. 소수 캐리어의 밀도를 보면 전자가 양공보다 많음

○ B-C 접합 : 다이오드로 볼 수 있음. 평형 상태로 간주할 수 있음

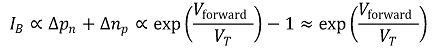

○ 베이스 전류 : 다이오드의 순방향 바이어스에서의 전류 식을 이용

○ 컬렉터 전류 : 대부분이 확산전류임을 이용. VBE에만 의존 (단, WB는 베이스의 두께)

○ 베이스 전류가 0이 아닌 이유

○ pB-E boundary를 만들기 위해 베이스에서 이미터로 이동하는 양공의 존재

○ 베이스에서 전자와 결합하는 양공

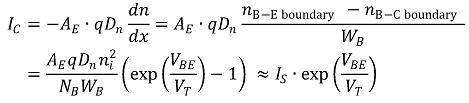

○ 결론

④ 등가회로 : B-E 접합은 문턱 전압을 갖는 다이오드로 모델링. B-C 접합은 종속 전류원으로 치환

○ 종속 전류원 : IC = βIB

○ 일반적으로 β는 정수이고 α는 아니므로 β를 많이 사용함

○ 전류는 컬렉터에서 이미터 쪽으로만 흐를 수 있음. 역방향 불가

○ 증폭비 β는 베이스의 물리적 크기와 도핑 농도에 따라 달라지며 일반적으로 100 정도

○ 발상 : 컬렉터를 통해 들어오려는 전류가 많은데 IB에 비례하는 정도만 컬렉터로 들어올 수 있음

○ 트랜지스터의 도통상태를 유지하기 위해 계속 베이스 전류가 흐르고 있어야 함

○ 문제 풀이 방법론 : 베이스 전류 → 컬렉터 전류 → 이미터 전류 → VCE → VCB 순으로 계산

⑷ 영역 2. 포화영역(saturation region)

① 조건 (NPN 트랜지스터 기준)

○ B-E 접합은 순방향 바이어스

○ B-C 접합은 순방향 바이어스

○ 즉, VE, VC < VB일 것

○ VBC < 400 mV인 경우 soft saturation, VBC > 400 mV인 경우 deep saturation이라고 함

② B-E에서 순방향 다이오드, C-E에서 순방향 다이오드가 있는 것과 같음

○ 내부적으로 전하 캐리어가 베이스 영역에 모여 포화됨 → 베이스 전류가 증가해도 컬렉터 전류흐름 변화 ×

○ B-E의 문턱전압은 일반적인 다이오드의 문턱전압과 같음 : 약 0.7 V

○ C-E의 문턱전압은 VCE(sat)로 표시하며 약 0.2 V

○ B 단자는 좁으므로 C-B의 순방향 바이어스는 곧 C-E의 순방향 바이어스와 같아짐

③ 등가회로

Figure. 5. 포화영역의 등가회로

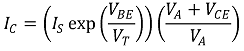

○ 기본적으로 VCE의 증가에 따라 IC가 지수적으로 증가 (Shockley 다이오드 모델)

○ 동작점 분석까지 고려하면 순방향 다이오드를 정전압원과 이상적 다이오드로 간주해도 무방 (정전압 특성곡선)

○ VBE가 일정한 것처럼 VCE(sat) 또한 일정함 : 이는 특성곡선을 단순화한 것

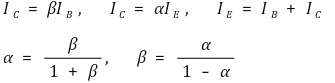

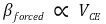

○ βforced는 컬렉터 전류 ÷ 베이스 전류로 정의

○ βforced는 VCE에 비례하여 증가 : 완벽한 비례 관계는 아님

○ βforced가 활성영역의 전류증폭비인 βdc까지 증가하면 활성영역으로 전환

⑸ 영역 3. 차단영역(cutoff region)

① 조건 (NPN 트랜지스터 기준)

○ B-E 접합은 역방향 바이어스

○ B-C 접합은 역방향 바이어스

○ 즉, VB < VE, VC일 것

② 등가회로

Figure. 6. 차단영역의 등가회로

⑹ 영역 4. 역방향 능동영역(역활성 영역, breakdown region)

① 조건 (NPN 트랜지스터 기준)

○ B-E 접합은 역방향 바이어스

○ B-C 접합은 순방향 바이어스

○ 즉, VE > VB > VC일 것

② 신호를 축소하므로 잘 사용하지 않는 영역

⑺ 트랜지스터의 전류-전압 특성 곡선 : 컬렉터의 전류-전압 특성 곡선이라고도 함

① 이상적 트랜지스터의 전류-전압 특성 곡선 : 컬렉터의 전류-전압 특성 곡선

Figure. 8. 단순화된 트랜지스터의 전류-전압 특성 곡선

○ 포화영역 : A ~ B. 즉, 기울기가 있는 선분 상에 있는 경우

○ VB = 0.7 V

○ VBB를 고정시키고 VCC를 증가시켜서 VCE를 0 ~ 0.7 V까지 점차로 증가

○ VC = VCE < VB = 0.7이므로 BC 접합은 순방향 바이어스 상태

○ VCC를 증가시켜 VCE가 증가하면 IC도 점차 증가 (Shockley 다이오드 모델) : 지수적으로 증가

○ IB를 증가시켜도 IC는 일정 : BE 접합과 BC 접합은 모두 순방향 바이어스이므로 제어 기능이 없음 (스위치 ON)

○ 등가회로에서 VCE가 일정한 것은 실제 다이오드를 이상적 다이오드 + 정전압원으로 나타내는 것과 유사. 즉, 그래프의 실질적 차이가 있지만 동작점 계산 시 크게 다르지 않은 해를 보여줌

○ 등가회로는 IC가 IB와 관련 없어서 선이 겹치게 됨. 실제 회로는 IB가 클수록 컬렉터 전류가 더 원활히 흐름

○ 활성영역 : B ~ C. 즉, 평행한 선분 상에 있는 경우

○ VB = 0.7 V

○ VCC를 증가시켜서 VCE > 0.7 V로 만듦

○ VC = VCE > VB = 0.7이므로 BC 접합은 역방향 바이어스 상태

○ VCC가 증가해도 IC는 일정하게 유지 : IC = β × IB, β = 상수

○ IB를 증가하면 IC 증가

○ 항복영역 : C 이후. 즉, 다시 기울기가 있는 반직선 상에 있는 경우

○ VCC가 계속 증가하여 BC 접합이 과도하게 역방향 바이어스가 되면 항복현상 발생 : 다이오드와 유사

○ 항복영역에서 트랜지스터는 파괴되므로 VCC < VCE(max)에서 사용할 것

○ 차단영역 : IB = 0

○ VBB = 0, IB = 0인 경우 VCC를 증가시키면 BC 접합과 BE 접합은 역방향 바이어스

○ 컬렉터 전류는 약간의 누설전류만 존재 : IC ≒ 0

○ BJT 트랜지스터가 IB로 제어된다는 말은 특성곡선이 IB를 고정한 상태에서 그려지기 때문

② 얼리 효과(early effect)

Figure. 10. 실제 트랜지스터의 전류-전압 특성 곡선

○ 베이스폭 변조효과(base-width modulation)라고도 함

○ VCE가 증가하면 컬렉터-베이스 역방향 접합의 공핍영역이 증가하고 유효 베이스 두께 WB가 감소함

○ 그 결과 컬렉터 전류가 증가함

○ 얼리 전압(early voltage) : 여러 기울어진 특성곡선을 연장하면 한 점에서 만나는데, 이때의 전압의 절댓값

③ 부하선과 동작점

○ 베이스 전류-전압, 컬렉터 전류-전압 각각에 대한 특성 곡선과 부하선의 교점을 동작점(Q point)이라고 함

○ 베이스 전류-전압 특성 곡선은 다이오드와 같음

○ 위 전류-전압 특성 곡선은 포화영역에서 IC가 IB에 약간 영향을 받는다는 점을 간과하였음

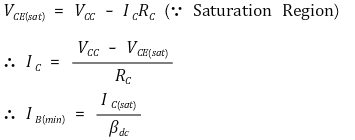

⑻ 응용 : 트랜지스터 스위치

① 정의 : 차단영역과 포화영역을 오가도록 바이어스를 세팅한 것

② 컬렉터 포화 전압을 알면 포화 영역 동작을 위한 최소 베이스 전류를 알 수 있음 (참고. ⑼-③)

⑼ 응용 : 광 트랜지스터

① 트랜지스터의 베이스에 도체를 연결하는 대신 빛을 받아 광전류가 흐르도록 만든 것

⑽ 요약

① 문제 풀이는 활성영역 → 차단영역 → 포화영역 순으로 품

② 접근 방법론 1. 전압 바이어스를 통해 판단

Figure. 12. 트랜지스터 작동영역(transistor region of operation)

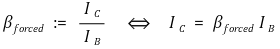

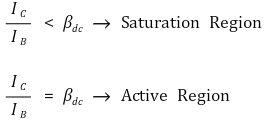

③ 접근 방법론 2. 포화영역과 활성영역을 구분할 때 베이스 전류에 대한 컬렉터 전류의 비로 판단

○ βforced < βdc이므로 다음과 같은 관계식이 관찰

○ 위 관계식을 기준으로 작동영역을 판단하는 것은 접근 방법론 1과 필요충분조건

○ 위 관계식을 이용하여 베이스에 전류원을 달아서 포화영역과 활성영역을 조절하기도 함

○ 위 관계식을 이용하여 포화영역에서 작동하기 위한 IB의 최솟값을 계산할 수 있음

3. 전계효과형 트랜지스터(FET, field effect transistor) [목차]

⑴ 정의 : 도체, 부도체, 반도체를 결합하여 제조

⑵ BJT 트랜지스터와의 비교

① 용어

○ BJT 트랜지스터의 이미터, 베이스, 컬렉터는 FET 트랜지스터의 소스(source), 게이트(gate), 드레인(drain)과 대응

○ BJT 트랜지스터가 NPN을 기준으로 한 것처럼, FET 트랜지스터는 n channel FET을 기준으로 함

○ FET에서 전하는 소스에서 드레인으로 이동 : n channel FET 기준, 전류는 드레인 → 소스. 전자는 소스 → 드레인

② BJT 트랜지스터의 제어 : 베이스 전류에 의해 제어됨

○ 대류 전류 : 전자, 정공, 전해액 내 이온과 같은 하전 입자의

③ FET 트랜지스터의 제어 : 게이트와 소스 사이의 전압으로 제어

○ 전도 전류 : 도체 내에서 전계의 작용으로 자유 전자의 이동이 생기는 것

○ 전자가 정공보다 이동성이 높음

○ 도핑된 반도체에서 다수 캐리어 쪽만 신경쓰면 됨

④ 장점 : 스위칭 속도가 매우 빠름

⑤ 단점 : 용량이 적어서 비교적 작은 전력 범위 내에서 기능

⑶ 종류 1. J-FET(junction FET)

① N 채널 J-FET

○ 게이트에 음의 전압을 걸면 P형 반도체에 있는 양공이 가장자리로 이동하면서 드레인 전류 증가

○ 게이트에 양의 전압을 걸면 P형 반도체에 있는 양공이 중앙으로 이동하면서 드레인 전류 감소

② P 채널 J-FET : N 채널 J-FET와 하는 일이 같으며 인가 전압이 반대

⑷ 종류 2. MOS-FET(metal oxider silicon FET) : J-FET보다 자주 사용됨

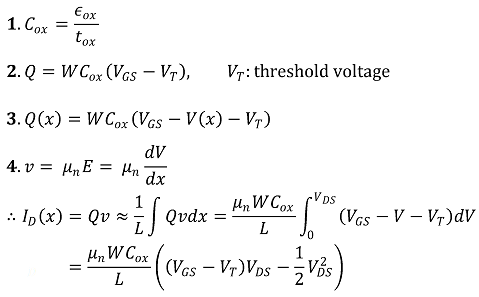

① 게이트가 절연체인 SiO2에 의해 드레인 및 소스로부터 분리된 형태

○ 기능 : 절연(insulation) 기능을 수행. 게이트로 오가는 전하의 흐름을 방지

○ 일종의 커패시터로 작용 : 아래 메커니즘 참고

② SiO2에는 폴리실리콘 또는 금속이 부착돼 있음 : 게이트의 전압이 골고루 퍼질 수 있게 함

③ 공핍형과 증가형으로 구분

④ CMOS(complementary MOS)

○ 대부분의 디지털 시스템은 CMOS 기술에 기초함

○ C는 상호보완성(complementary)을 나타냄 : p형과 n형이 있기 때문

○ n channel MOS를 n type MOS 또는 nMOS라고도 함

○ p channel MOS를 p type MOS 또는 pMOS라고도 함

○ 반드시 nMOS는 GND에, pMOS는 voltage source에 연결돼도록 해야 함

⑸ 종류 2-1. 증가형 MOS-FET(E MOS-FET, enhancement type MOS-FET)

Figure. 15. 증가형 MOS-FET 기호

① n channel E MOS-FET을 기준으로 설명

② 1st. 기본적으로 드레인과 소스 사이에는 NPN 반도체가 있어서 전류가 흐를 수 없음

③ 2nd. 채널 형성 : 게이트 전극에 소스보다 큰 전압을 인가하면 산화막 아래에 전자들이 모여 반전층 형성

○ 커패시터 동작 : 커패시터의 경우 한쪽이 (+)이면 반대쪽은 (-)인 것을 상기

④ E MOS-FET 문턱전압 (VT, VTH)

○ E MOS-FET에서 채널을 형성하기 위한 최소 게이트 전압

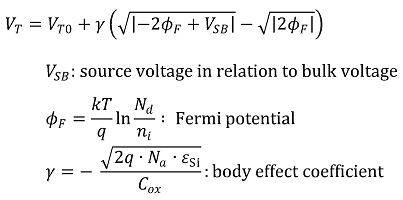

○ 바디 효과(body effect) : VT가 증가하는 요인. PMOS 기준, 바디 효과를 나타내는 식은 다음과 같음

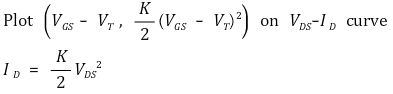

⑤ 포화영역(saturation region)

○ 조건 1. VGS - VT < 드레인 전압(VDS)

○ 조건 2. 게이트 전압(VGS) - 문턱전압(VT) > 0

○ 위 조건은 마치 게이트와 소스가 순방향 바이어스이고, 게이트와 드레인이 역방향 바이어스인 상황

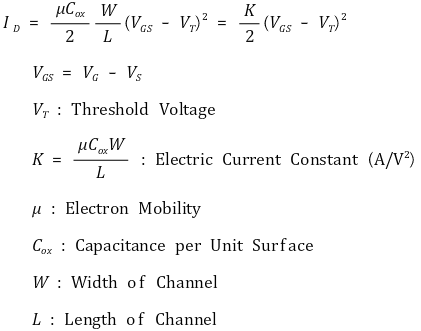

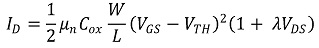

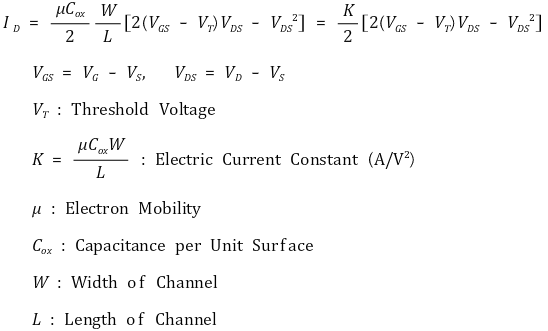

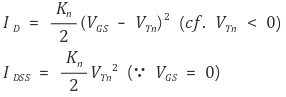

○ 전류 특성 : 전류 상수 K는 제조 시점에서 이미 결정돼 있음

○ 드레인 전압은 전자의 운동뿐만 아니라 채널의 형태를 바꿈

Figure. 16. 드레인 전압의 인가와 채널의 형태 변화

○ 핀치오프(pinch-off) 현상 : 채널 내의 전자들이 드레인으로 빠져나가다가 채널이 끊기는 현상

○ (주석) 채널이 끊기면 전류가 흐르지 않는다는 의미

○ (주석) 적당히 끊겼다 안 끊겼다를 조절하면서 드레인-소스 전압에 무관하게 전류가 흐른다는 걸로 추정

○ channel length modulation : 유효 채널 길이가 짧아져 드레인 전류가 증가함

○ BJT 트랜지스터의 활성영역은 FET 트랜지스터의 포화영역과 대응

⑥ 비포화영역(Ohmic region)

○ 조건 1. 드레인 전압(VDS) < VGS - VT

○ 조건 2. 게이트 전압(VGS) - 문턱전압(VT) > 0

○ 위 조건은 마치 게이트와 소스가 순방향 바이어스이고, 게이트와 드레인이 순방향 바이어스인 상황

○ 전류 특성 : 전류 상수 K는 제조 시점에서 이미 결정돼 있음

○ 전류 식 유도

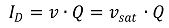

○ carrier velocity saturation : L이 매우 작거나 E가 매우 클 때 전류 식은 다음과 같이 됨

○ BJT 트랜지스터의 포화영역은 FET 트랜지스터의 비포화영역과 대응

⑦ 차단영역

○ 조건 : 게이트 전압(VGS) - 문턱전압(VT) < 0

○ 위 조건은 마치 게이트와 소스가 역방향 바이어스인 상황

○ 게이트 전압이 E MOS-FET 문턱전압을 넘지 못해 채널 형성이 안 됨 → 전류 흐르지 않음

⑧ 특성곡선

○ 비포화영역 : 기울기가 있는 선분 상에 있는 점들

○ 포화영역 : 평행한 반직선 지점. 실제로는 얼리효과가 관찰돼 약간의 기울기가 있음

○ 차단영역 : ID = 0

○ 드레인 전류 ID는 BJT 트랜지스터의 컬렉터 전류 IC와 대응

○ 드레인-소스 전압 VDS는 BJT 트랜지스터의 컬렉터-이미터 전압 VCE와 대응

○ 천이점 : 불포화영역과 포화영역의 경계

○ FET 트랜지스터가 VGS로 제어된다는 말은 특성곡선이 VGS를 고정한 상태에서 그려지기 때문

⑨ 요약 : 문제가 주어졌을 때 포화영역 → 비포화영역 → 차단영역 순으로 상황을 가정해야 함

⑹ 종류 2-2. 공핍형 MOS-FET(D MOS-FET, depletion type MOS-FET)

① n channel D MOS-FET을 기준으로 설명

② 1st. 구조적으로 채널이 이미 형성돼 있음 : 게이트 전압이 없어도 드레인 전류가 흐름

○ n형 반도체가 실리콘 산화막 아래에 얇게 깔려 있음

③ 2nd. 게이트 전압이 양의 전압인 경우 n형 반도체의 전자가 산화막 아래로 모임

○ 커패시터 동작 : 커패시터의 경우 한쪽이 (+)이면 반대쪽은 (-)인 것을 상기

○ 전자가 산화막 아래로 모이면서 채널이 두꺼워짐 → 전류가 강화됨

○ 전류가 증가하는 것을 증가형 모드 동작이라고 함

④ 3rd. 게이트 전압이 음의 전압인 경우 n형 반도체의 전자가 가장자리로 흩어짐

○ 커패시터 동작 : 커패시터의 경우 한쪽이 (-)이면 반대쪽은 (+)인 것을 상기

○ 전자가 산화막 아래에서 가장자리로 흩어지면서 채널이 얇아짐 → 전류가 약화됨

○ 전류가 감소하는 것을 공핍형 모드 동작이라고 함

⑤ D MOS-FET 문턱전압 : 드레인 전류를 0으로 만드는 전압

○ VGS = 0인 경우에도 드레인 전류는 0이 아님 : 이때의 전류를 IDSS라고 함

⑥ 특성곡선

Figure. 21. D MOS-FET의 특성곡선

Figure. 22. D MOS-FET의 특성곡선

입력 : 2018.02.15 14:33

수정 : 2022.09.11 21:48

'▶ 자연과학 > ▷ 회로이론' 카테고리의 다른 글

| 【회로이론】 10강. Op Amp (2) | 2019.11.25 |

|---|---|

| 【회로이론】 9강. 반도체 증폭회로 (0) | 2019.11.25 |

| 【회로이론】 7강. 다이오드 (1) | 2019.11.08 |

| 【회로이론】 5-3강. 함수 생성기(function generator) 사용법 (0) | 2016.09.24 |

| 【회로이론】 5-2강. 오실로스코프(oscilloscope) 사용법 (0) | 2016.09.24 |

최근댓글